- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

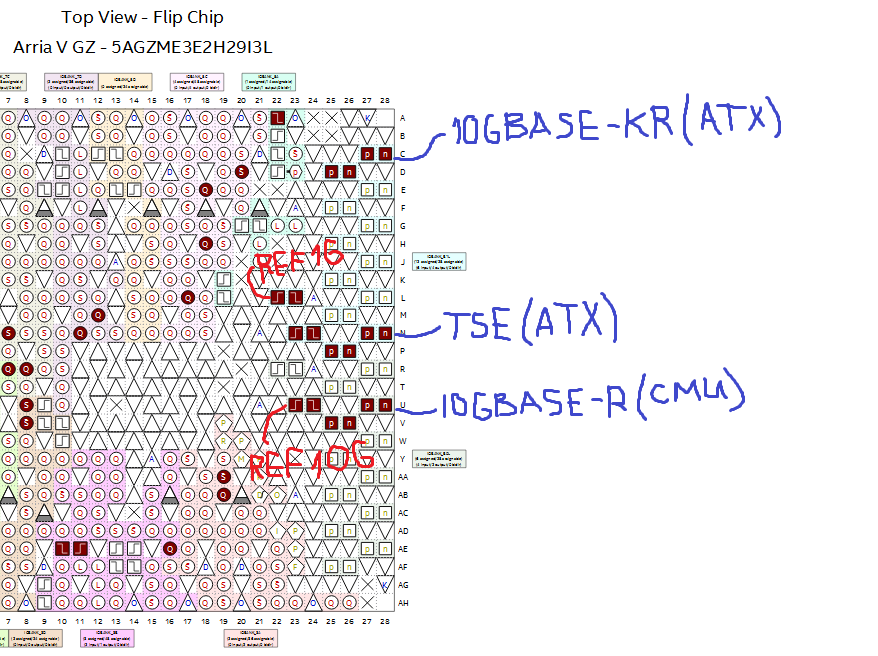

I'm having fun with the transceiver once again. I am trying to set up a simple config in Arria VGZ:

10GBASE-KR (10G, AN, LT, 644 MHz ref, ATX PLL), TSE (ATX PLL), 10GBASE-R (CMU PLL).

I fit it like this:

But quartus gave errors:

Error (14566): The Fitter cannot place 2 periphery component(s) due to conflicts with existing constraints (2 HSSI PMA Aux. block(s)). Fix the errors described in the submessages, and then rerun the Fitter. The Intel FPGA Knowledge Database may also contain articles with information on how to resolve this periphery placement failure. Review the errors and then visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

Error (175020): The Fitter cannot place logic HSSI PMA Aux. block that is part of Triple-Speed Ethernet Intel FPGA IP GBE_net_cpi_TSE_ATX_eth_tse_0 in region (0, 48) to (0, 48), to which it is constrained, because there are no valid locations in the region for logic of this type.

Info (14596): Information about the failing component(s):

Info (175028): The HSSI PMA Aux. block name(s): GBE_net_cpi:GBE_net_cpi_0|GBE_net_cpi_TSE_ATX:ETH_gen[1].TSE_ATX|GBE_net_cpi_TSE_ATX_eth_tse_0:eth_tse_0|altera_xcvr_custom:i_custom_phyip_0|sv_xcvr_custom_nr:S5|sv_xcvr_custom_native:transceiver_core|sv_xcvr_native:gen.sv_xcvr_native_insts[0].gen_bonded_group.sv_xcvr_native_inst|sv_pma:inst_sv_pma|sv_tx_pma:tx_pma.sv_tx_pma_inst|sv_tx_pma_ch:tx_pma_insts[0].sv_tx_pma_ch_inst|tx_pma_ch.tx_pma_buf.tx_pma_aux

Info (175013): The HSSI PMA Aux. block is constrained to the region (0, 48) to (0, 48) due to related logic

Info (175015): The I/O pad gxb_tx[1] is constrained to the location PIN_P25 due to: User Location Constraints (PIN_P25)

Info (14709): The constrained I/O pad is driven by this HSSI PMA Aux. block

Error (11238): The following 1 HSSI PMA Aux. block locations are already occupied, and the Fitter cannot merge the previously placed nodes with these instances. The nodes may have incompatible inputs or parameters.

Error (11239): Location HSSIPMAAUX_X0_Y48_N93 is already occupied by GBE_net_cpi:GBE_net_cpi_0|PHY_KR_cpi:PHY_10GBASE_KR_gen.PHY_KR_cpi|PHY_KR_cpi_10GBASE_KR:phy_kr_gen[0].PHY_KR_cpi_10GBASE_KR|altera_xcvr_10gbase_kr:xcvr_10gbase_kr_0|altera_xcvr_native_sv:SV_NATIVE.altera_xcvr_native_sv_inst|sv_xcvr_native:gen_native_inst.xcvr_native_insts[0].gen_bonded_group_native.xcvr_native_inst|sv_pma:inst_sv_pma|sv_tx_pma:tx_pma.sv_tx_pma_inst|sv_tx_pma_ch:tx_pma_insts[0].sv_tx_pma_ch_inst|tx_pma_ch.tx_pma_buf.tx_pma_aux.

Info (175013): The HSSI PMA Aux. block is constrained to the region (0, 48) to (0, 48) due to related logic

Info (175015): The I/O pad gxb_tx[0] is constrained to the location PIN_D25 due to: User Location Constraints (PIN_D25)

Info (14709): The constrained I/O pad is driven by this HSSI PMA Aux. block

Error (21087): Input port "CALCLK" must be driven by the same source

Info (21090): Atom "GBE_net_cpi:GBE_net_cpi_0|GBE_net_cpi_TSE_ATX:ETH_gen[1].TSE_ATX|GBE_net_cpi_TSE_ATX_eth_tse_0:eth_tse_0|altera_xcvr_custom:i_custom_phyip_0|sv_xcvr_custom_nr:S5|sv_xcvr_custom_native:transceiver_core|sv_xcvr_native:gen.sv_xcvr_native_insts[0].gen_bonded_group.sv_xcvr_native_inst|sv_pma:inst_sv_pma|sv_tx_pma:tx_pma.sv_tx_pma_inst|sv_tx_pma_ch:tx_pma_insts[0].sv_tx_pma_ch_inst|tx_pma_ch.tx_pma_buf.tx_pma_aux" is driven by source "~GND"

Info (21090): Atom "GBE_net_cpi:GBE_net_cpi_0|PHY_KR_cpi:PHY_10GBASE_KR_gen.PHY_KR_cpi|PHY_KR_cpi_10GBASE_KR:phy_kr_gen[0].PHY_KR_cpi_10GBASE_KR|altera_xcvr_10gbase_kr:xcvr_10gbase_kr_0|altera_xcvr_native_sv:SV_NATIVE.altera_xcvr_native_sv_inst|sv_xcvr_native:gen_native_inst.xcvr_native_insts[0].gen_bonded_group_native.xcvr_native_inst|sv_pma:inst_sv_pma|sv_tx_pma:tx_pma.sv_tx_pma_inst|sv_tx_pma_ch:tx_pma_insts[0].sv_tx_pma_ch_inst|tx_pma_ch.tx_pma_buf.tx_pma_aux" is driven by source "clk_125MHz~inputCLKENA0"

Error (175020): The Fitter cannot place logic HSSI PMA Aux. block that is part of Triple-Speed Ethernet Intel FPGA IP GBE_net_cpi_TSE_ATX_eth_tse_0 in region (0, 48) to (0, 48), to which it is constrained, because there are no valid locations in the region for logic of this type.

Info (14596): Information about the failing component(s):

Info (175028): The HSSI PMA Aux. block name(s): GBE_net_cpi:GBE_net_cpi_0|GBE_net_cpi_TSE_ATX:ETH_gen[1].TSE_ATX|GBE_net_cpi_TSE_ATX_eth_tse_0:eth_tse_0|altera_xcvr_custom:i_custom_phyip_0|sv_xcvr_custom_nr:S5|sv_xcvr_custom_native:transceiver_core|sv_xcvr_native:gen.sv_xcvr_native_insts[0].gen_bonded_group.sv_xcvr_native_inst|sv_pma:inst_sv_pma|sv_rx_pma:rx_pma.sv_rx_pma_inst|rx_pmas[0].rx_pma.rx_pma_aux

Info (175013): The HSSI PMA Aux. block is constrained to the region (0, 48) to (0, 48) due to related logic

Info (175015): The I/O pad gxb_rx[1] is constrained to the location PIN_N27 due to: User Location Constraints (PIN_N27)

Info (14709): The constrained I/O pad contains a HSSI PMA RX Buffer, which is driven by this HSSI PMA Aux. block

Error (11238): The following 1 HSSI PMA Aux. block locations are already occupied, and the Fitter cannot merge the previously placed nodes with these instances. The nodes may have incompatible inputs or parameters.

Error (17932): Location HSSIPMAAUX_X0_Y48_N93 is already occupied by 2 HSSI PMA Aux. blocks

Info (11237): Already placed at this location: GBE_net_cpi:GBE_net_cpi_0|PHY_KR_cpi:PHY_10GBASE_KR_gen.PHY_KR_cpi|PHY_KR_cpi_10GBASE_KR:phy_kr_gen[0].PHY_KR_cpi_10GBASE_KR|altera_xcvr_10gbase_kr:xcvr_10gbase_kr_0|altera_xcvr_native_sv:SV_NATIVE.altera_xcvr_native_sv_inst|sv_xcvr_native:gen_native_inst.xcvr_native_insts[0].gen_bonded_group_native.xcvr_native_inst|sv_pma:inst_sv_pma|sv_tx_pma:tx_pma.sv_tx_pma_inst|sv_tx_pma_ch:tx_pma_insts[0].sv_tx_pma_ch_inst|tx_pma_ch.tx_pma_buf.tx_pma_aux

Info (175013): The HSSI PMA Aux. block is constrained to the region (0, 48) to (0, 48) due to related logic

Info (175015): The I/O pad gxb_tx[0] is constrained to the location PIN_D25 due to: User Location Constraints (PIN_D25)

Info (14709): The constrained I/O pad is driven by this HSSI PMA Aux. block

Info (11237): Already placed at this location: GBE_net_cpi:GBE_net_cpi_0|PHY_KR_cpi:PHY_10GBASE_KR_gen.PHY_KR_cpi|PHY_KR_cpi_10GBASE_KR:phy_kr_gen[0].PHY_KR_cpi_10GBASE_KR|altera_xcvr_10gbase_kr:xcvr_10gbase_kr_0|altera_xcvr_native_sv:SV_NATIVE.altera_xcvr_native_sv_inst|sv_xcvr_native:gen_native_inst.xcvr_native_insts[0].gen_bonded_group_native.xcvr_native_inst|sv_pma:inst_sv_pma|sv_rx_pma:rx_pma.sv_rx_pma_inst|rx_pmas[0].rx_pma.rx_pma_aux

Info (175013): The HSSI PMA Aux. block is constrained to the region (0, 48) to (0, 48) due to related logic

Info (175015): The I/O pad gxb_rx[0] is constrained to the location PIN_C27 due to: User Location Constraints (PIN_C27)

Info (14709): The constrained I/O pad contains a HSSI PMA RX Buffer, which is driven by this HSSI PMA Aux. block

Error (21087): Input port "CALCLK" must be driven by the same source

Info (21090): Atom "GBE_net_cpi:GBE_net_cpi_0|GBE_net_cpi_TSE_ATX:ETH_gen[1].TSE_ATX|GBE_net_cpi_TSE_ATX_eth_tse_0:eth_tse_0|altera_xcvr_custom:i_custom_phyip_0|sv_xcvr_custom_nr:S5|sv_xcvr_custom_native:transceiver_core|sv_xcvr_native:gen.sv_xcvr_native_insts[0].gen_bonded_group.sv_xcvr_native_inst|sv_pma:inst_sv_pma|sv_rx_pma:rx_pma.sv_rx_pma_inst|rx_pmas[0].rx_pma.rx_pma_aux" is driven by source "~GND"

Info (21090): Atom "GBE_net_cpi:GBE_net_cpi_0|PHY_KR_cpi:PHY_10GBASE_KR_gen.PHY_KR_cpi|PHY_KR_cpi_10GBASE_KR:phy_kr_gen[0].PHY_KR_cpi_10GBASE_KR|altera_xcvr_10gbase_kr:xcvr_10gbase_kr_0|altera_xcvr_native_sv:SV_NATIVE.altera_xcvr_native_sv_inst|sv_xcvr_native:gen_native_inst.xcvr_native_insts[0].gen_bonded_group_native.xcvr_native_inst|sv_pma:inst_sv_pma|sv_tx_pma:tx_pma.sv_tx_pma_inst|sv_tx_pma_ch:tx_pma_insts[0].sv_tx_pma_ch_inst|tx_pma_ch.tx_pma_buf.tx_pma_aux" is driven by source "clk_125MHz~inputCLKENA0"

Please decrypt what is the problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Thanks for your update and test results. If I understand it correctly, the PMA AUX is the calibration block. For your information, you would need to connect reconfiguration controller to all the transceiver instances so that the offset cancellation can be performed to ensure correct funtionality of the transceivers. You can share the reconfiguration controller for them to save logic and test if can pass Fitter compilation. Please let me know if there is any concern. Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you observe some Fitter errors when trying to fit your design with two 10G PHYs and one TSE IP. By merely looking at the error messages, seems like it is related to the AUX block. Can you try with the following:

1. Share the reconfiguration interface input ports ie clock, reset, address, write and etc among the 3 instances to see if it helps.

2. If your selected device has XCVR on both side, try moving the TSE to a different side of the 10G PHYs to help narrow down if it is due to the TSE IP?

3. If the above still not working, please share with me a simple test design with the 3 instances which can replicate the error for further debugging. Please let me know the Quartus version that you are using as well.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your feedback.

The problem is really with HSSI_PMA_AUX block. By the way, what is this block? Calibration block?

I simplified my project as much as possible. Left only Ethernet Backplane 10GBASE-KR with reconfiguration controller and 10GBASE-R without reconfiguration controller. And I understand that when they are in the same transceiver bank (in different triplet) - error with AUX block occurs. When they are in different banks everything is ok.

Did I understand correctly that this is happening because I have not connected 10GBASE-R with reconfig controller? it's just that I don't need to connect the second PHY to reconfig controller (only first PHY) and i did not want spend logic on it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Thanks for your update and test results. If I understand it correctly, the PMA AUX is the calibration block. For your information, you would need to connect reconfiguration controller to all the transceiver instances so that the offset cancellation can be performed to ensure correct funtionality of the transceivers. You can share the reconfiguration controller for them to save logic and test if can pass Fitter compilation. Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just would like to follow up with you if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I understand it, it has been some time since I last heard from you. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page