- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

we are using stratix 10 GX dev kit and quartus prime pro 18.1

ISSUE: HPS ddr4 is not booting

DDR4 is detecting but DDR4 clear failed

ddr4 calibration failed

we selected FPGA Configuration first method.

have downloaded example design from https://releases.rocketboards.org/release/2020.05/gsrd/s10_gsrd/

compared the project and found change is qsf for the pins

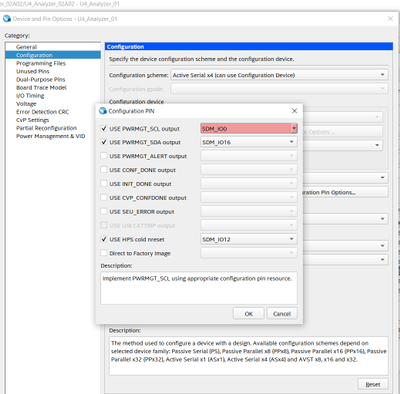

"set_global_assignment -name USE_PWRMGT_SCL SDM_IO0

set_global_assignment -name USE_PWRMGT_SDA SDM_IO16

set_global_assignment -name USE_HPS_COLD_RESET SDM_IO12"

Assignments ➤ Device ➤ Device and Pin Options ➤

Configuration Pin Options.

tried to change pins according to tool is not accepting the change(please see the attached snapshot)

other than this there is no change!

Teraterm log:

U-Boot SPL 2019.10-02883-ga2f8989-dirty (Aug 15 2020 - 15:14:38 +0530)

Reset state: Cold

MPU 1350000 kHz

L3 main 385714 kHz

Main VCO 2700000 kHz

Per VCO 2000000 kHz

EOSC1 25000 kHz

HPS MMC 48214 kHz

UART 96428 kHz

DDR: 4096 MiB

SDRAM-ECC: Initialized success with 896 ms

QSPI: Reference clock at 400000000 Hz

WDT: Not found!

Trying to boot from MMC1

U-Boot 2019.10-02883-ga2f8989-dirty (Aug 15 2020 - 15:14:38 +0530)socfpga_stratix10

CPU: Intel FPGA SoCFPGA Platform (ARMv8 64bit Cortex-A53)

Model: SoCFPGA Stratix 10 SoCDK

DRAM: 4 GiB

"Synchronous Abort" handler, esr 0x96000210

elr: 000000000005d6b4 lr : 000000000005dd0c (reloc)

elr: 000000007ff996b4 lr : 000000007ff99d0c

x0 : 000000007fa34fc3 x1 : 000000007fa34fc3

x2 : 00000000fffffffe x3 : 0000000000000020

x4 : 00000000ffffffff x5 : 0000000000000030

x6 : 000000007ffa8413 x7 : 000000000000000f

x8 : 00000000ffffffd0 x9 : 000000000000000c

x10: 0000000000000010 x11: 000000000000000c

x12: 0000000000000002 x13: 0000000000002150

x14: 00000000ffe3cd8c x15: 0000000000000008

x16: b0519d3b532f5bcb x17: 67effe077f86a67c

x18: 000000007fa3cdd8 x19: 000000007fa34fbb

x20: 0000000000000021 x21: 000000007fa357bd

x22: 0000000000000010 x23: 0000000000000000

x24: 0000000000000020 x25: 0000000000000000

x26: 00000000ffffffff x27: 000000007ffa86a8

x28: 000000007fa34fbb x29: 000000007fa34d60

Resetting CPU ...

### ERROR ### Please RESET the board ###

-------------------------------------------------------------------------

As tool is not accepting the change, tool is upgraded to 21.1

and 1)generated .sof and .jic file in 21.1 where data is not printing on tera term(boot failed)

2).sof (21.1) created .jic(18.1) with this we boot is successful.

- i) .sof (18.1) created .jic(18.1) boot = failed

- i) .sof (21.1) created .jic(21.1) boot = failed

iii).sof (21.1) created .jic(18.1) with this we boot is successful.

boot is successful but we are not able to use Signaltap nor transceiver tool kit!

Two options are tried for u-boot

1. GHRD based. Taken from : https://releases.rocketboards.org/release/2020.05/gsrd/s10_gsrd/

"u-boot-spl-dtb.hex" is used to generate .jic

---> Working

2. Using rocketboards reference design provided. U-boot is built by following below instructions

git clone https://github.com/altera-opensource/u-boot-socfpga

cd u-boot-socfpga

git checkout -b test ACDS20.1_REL_GSRD_PR

make clean && make mrproper

make socfpga_stratix10_defconfig

make -j 24

The following files will be created in respective directories:

• $TOP_FOLDER/u-boot-socfpga/u-boot.img - U-Boot image file

• $TOP_FOLDER/u-boot-socfpga/spl/u-boot-spl-dtb.hex - SSBL/SPL hex file

"u-boot-spl-dtb.hex" is used to generate .jic

---> This also works

With Quartus prime pro 18.1 version for .jic file generation

and .sof file for Quartus prime pro 21.1 version

For your information : uboot generation may not causing the issue,

as we used .sof from https://releases.rocketboards.org/release/2020.05/gsrd/s10_gsrd/

and created .jic using our .hex file with prime Quartus pro 18.1 version

--> this worked.

BUT the same tried with Quartus prime pro 21.1 version it is failing.

queries:

1) In quartus prime pro 18.1 what can cause for not accepting the values ?(PFA)

2) .jic file created in 21.1 (followed procedure given in datasheet) but still boot failed.

3).sof (21.1) created .jic(18.1) with this we boot is successful.

.jic with 21.1 is not booting, what can go wrong!

created .jic with .sof & .hex provided by GHRD in 21.1 boot is failing

created .jic with .sof & .hex provided by GHRD in 18.1 boot is successful

what is wrong in 21.1 tool ?

why .jic created in 21.1 is failing ?

Regards,

Rajesh

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

How did you generated the jic file? Are you using the GUI/quartus_cpf/quartus_pfg?

Have you tried all without the changes, will all test past if no changes made? (All are default)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We have followed :1.3.1.2. Step 2: Generate Secondary Programming Files (Programming File

Generator) from intel document for generation of .jic file.

As our devkit heating issue, we will continue testing after few days.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page