- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I try to communicate with a Micron Falsh attached to Arria10 FPGA with Generic Serial Flash Interface IP Core.

The part number of Flash is N25Q256A11E1240.

In my FPGA design I reset the IP Core then read CSR, which I expect to get the default values of CSR.

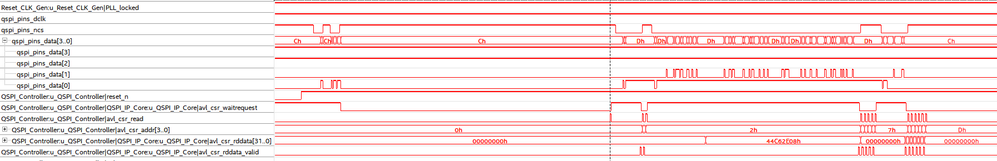

The following picture is a screenshot of stp, the capture clock is IP_CLK that drive the IP, currently the frequency is 100MHz.

Here are my questions:

1. I think the CSR is located in FPGA, reading CSR doesn't need to access Flash, why the qspi_pins_ncs is driven low when the FPGA starts a read CSR operation? Also the qspi_pins_data[1] and qspi_pins_data[0] toggle, indicates the data output from Flash.

2. According to the user guide, qspi_pins_dclk should be a division of IP_CLK, why the waveform of qspi_pins_dclk is continuous high?

3. Why the value of avl_csr_rddata isn't the defalut value when avl_csr_rddata_valid is high? I don't write anything into CSR, and I think the IP Core should output default values.

Any suggestions?

Thanks, regards.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SYiwe,

May I know how do you connect your avl_csr & avl_mem port in your design?

If possible Screenshot your Qsys design here.

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page