- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

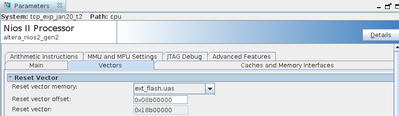

I have a reference NIOS project in which the reset vector memory is selected as an external flash. I opened platform designer and found the following information. Picture attached below.

Can you help to answer my following questions?. I did go through the embedded handbook, and NIOS user guide but could not get a specific answer. Can you help?

Q1) Why is the "reset vector" field greyed out here?.

Q2) Which address will be taken into account for the reset vector?. 0x08b0_0000 (or) 0x18b0_0000?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MK,

Greetings and welcome to Intel's forum.

There is not specific reason why it is greyed out. It is according to the base address you set in Platform Designer. You have the flash address set to 0x10000000, and the offset to 0x08b00000. Therefore, flash will start access at 0x18b00000.

Hope this clarifies your doubts.

Thank you.

Regards,

Kelly

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kelly,

I understand. You may close this ticket for now. I will reopen one if needed in future. Thanks for your support.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

Thank you.

Regards,

Kelly Jialin, GOH

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »