Hi- Everybody

I tested a chip.

Test is data in put and then other chip any signal output.

It was successful up to 4G.

In higher frequency than 4G failed.

But in fPLL GUI, wrote the some value "Desired Reference clock frequency"

i wrote the some value "Desired Reference clock frequency"

So, I was successful up to 4.8G.

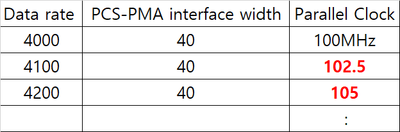

for example, written frequency is below

in data rate 4100, wrote 102.5MHz

in data rate 4200, wrote 105MHz

What is the meaning "Desired Reference clock frequency" ?

Desired Reference clock frequency is a valid values for reference clock frequency and it change with the data rate but the reference input clock frequency must be within 50 MHz and 622 MHz. Range of supported reference clock frequency is dependent on device. You may device datasheet for range of supported frequency for every device.

链接已复制

Desired Reference clock frequency is a valid values for reference clock frequency and it change with the data rate but the reference input clock frequency must be within 50 MHz and 622 MHz. Range of supported reference clock frequency is dependent on device. You may device datasheet for range of supported frequency for every device.

Let me know if there is any other concern at your end.

Otherwise I will put this ticket to close pending

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 5/5 survey