- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi everyone,

Im trying to read and write to ddr3 on the EVB cyclone v board.

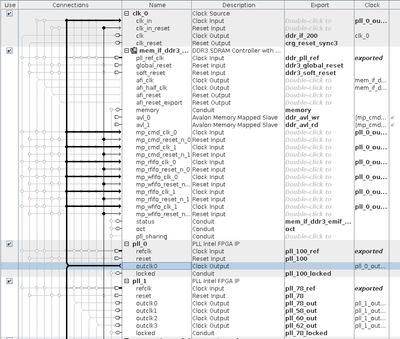

im using the ddr controller.

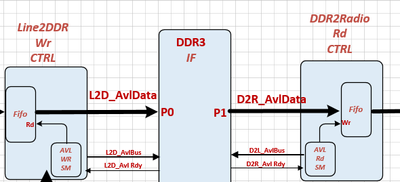

i created read and write components to the controller through the avalon bus:

platform designer connectivity:

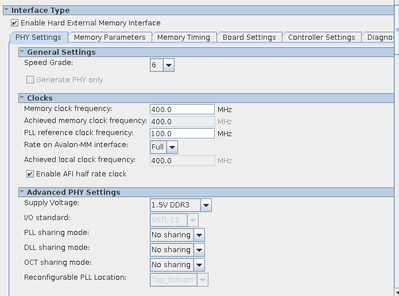

Im using hard ip controller with 400Mhz clock to ddr.

the ddr interface onboard has 32 bit data.

Im writing to ddr controller on avalon bus in 200Mhz clock 128bits of data , bursts of 4.

the write data flow is: data generator(10gbps) -> line2ddr_wr_ctrl -> ddr controller -> ddr.

the read data flow is: ddr -> ddr_controller -> ddr2radio_rd_ctrl (reading in 7.4gbps)

i managed to measure throughput of 17.4gbps. on simulation .

but in synthesis it seems that we are not over the 10gbps throughput.

what could be the reasons?

should we use arbiters between the avalon ctrl to the ddr controller?

maybe use different avalon clock?

BR,

Ram.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ram,

I need further information from your IP setting in order to debug in this case.

Can you provide the DDR IP setting together with the memory device datasheet?

There are some points that I can share with you at the moment to improve the performance.

- Try to increase the burst length if possible.

- Perform the read and write transaction in sequence. For example, perform all write transaction first and then read.

You can set the arbiter from Platform Designer to identify the first priority module.

Is there any timing issue in the design?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Adzim,

thank you for answering.

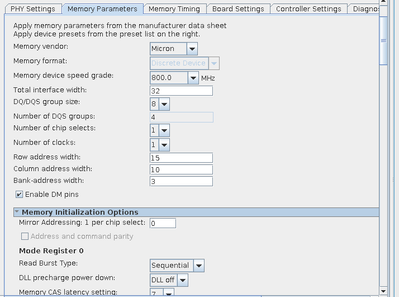

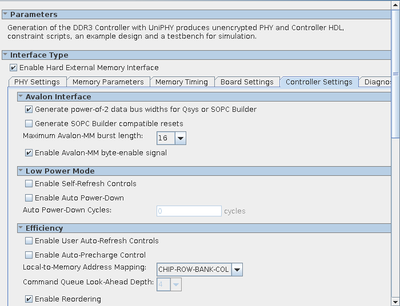

here are the settings for the ddr ip:

also, the board settings and memory timing are according to the evb cyclone v soc development kit.

the memory device is: mt41k256m16ha-125 x2 .

there were no timing issues regards to the ddr.

more details about the design:

we have 2 fifo's -one in the write side.and one on the read side.

we are writing with data counter that increments with clock of 78.125mhz(10gbps).

we are reading from the fifo on the write side in 200mhz (avalon bus).

we are reading from the fifo on the read side in 5gbps(can be change).

hope this is helpful,

just a reminder: in simulation everything works fine.

when we try to test it on board it does not .

BR,

Ram.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ram,

Thank you for your feedback.

You can improve the efficiency of the memory controller by enabling the auto-precharge control option.

If you turn on Enable Auto-Precharge Control, you can instruct the controller to issue an auto-prechagre read or write command. The next time you access that bank, the access is faster because the controlled does not have to precharge the bank before activating the row that you want to access.

The address ordering also can improve the controller efficiency.

- Choose Chip-Bank-Row-Col for random traffic.

- Choose Chip-Row-Bank-Col for sequential traffic.

- Choose Row-Chip-Bank-Col for sequential traffic and multiple chip selects.

From what I expect that the simulation result should be good, and the actual hardware may be slightly difference `because of the hardware connectivity and the memory device.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

I tried the auto-precharge control option but with no change.

also the address ordering.

it seems strange because we are talking about only 15 gbps throughput, when the maximum theoretical throughput is 25.6gbps with this chip and the memory devices.

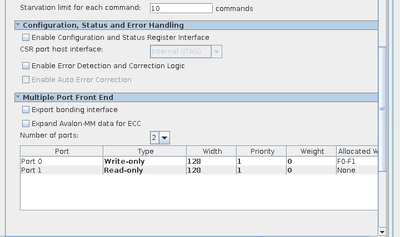

there could be difference in the throughput between using one port bidirectional, or two ports when one is for write only and the second is for read only?(see our ip settings).

I don't know where else to search,

I will appreciate if you find more options,

BR,

Ram.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ram,

There is no information on the advantage between the unidirectional and bidirectional ports.

But what I can see that the bidirectional port can guarantee the operation ordering.

- The requests arriving at a port are executed in order in which they are received.

- The requests arriving at different ports have no guaranteed order of service.

But the multi-port can have a scheduling by the priority and weight of a port.

- Any transactions of priority seven will always be scheduled before transactions of priority six or lower.

- If two ports have same priority value, the weight value will be updated.

- Let say the weight values have been set to 4 and 6.

- The port with a weight of 4 will receive 40% of bus bandwidth.

- The port with a weight of 6 will receive 60% of bus bandwidth.

- Assuming 100% total available bus bandwidth.

You can try to change the priority value and weight value of the ports and see if that improve the efficiency.

Also try to increase the Maximum Avalon-MM burst length to higher value.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank you for your reply Adzim.

we managed to solve the problem by changing from 2 ports to single port.

the throughput now is according to our expectations.

although still have timing issues we need to deal with.

thank you.

BR,

Ram.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page