- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi ,

I now directly control the function of emac through hps.

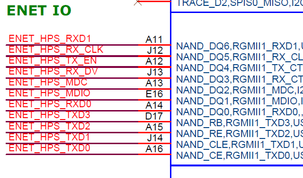

So the external PHY is directly connected to the I/O pin of hps, as shown in figure.

However, the speed of the ethernet is limited to less than 100Mbps due to the large image data to be transmitted.

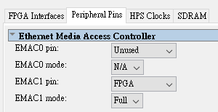

So I want to replace the function of image transmission through FPGA(and keep ethernet command control in hps), as shown in the figure below.

And the question I want to ask is:

1.Is there any way to allow FPGA to control the I/O of HPS without changing the PCB layout?

2.If this method can be achieved, will his speed be limited?

Thank you.

Lien copié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

Yes you can route to FPGA, though the speed limitation is always be affected and varied by designs itself.

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

Do you have further questions?

- S'abonner au fil RSS

- Marquer le sujet comme nouveau

- Marquer le sujet comme lu

- Placer ce Sujet en tête de liste pour l'utilisateur actuel

- Marquer

- S'abonner

- Page imprimable