- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am aiming to measure traffic across each common step mesh via uncore performance counters. I know that counter registers can be programmed to count traffic "entering" the tile they belong to.

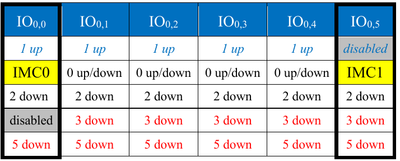

Below is an example from a technical paper of @McCalpinJohn.

However, there is something I did not quite understand. According to my understanding, it should not make sense for example for tiles on bottom (only the last row) to measure traffic on them in up direction, since there is no tiles below them. Similar story goes for leftmost and rightmost tiles as well.

What am I missing here?

Thanks and regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are missing some sneaky details that Intel has not talked about. It turns out that there is a very small amount of traffic through the three edges that one would expect to be idle (the top won't be idle because of IO).

My current interpretation is that this traffic is related to rare traffic collisions between traffic shifting from the vertical links to the horizontal links.

I have never seen more than a tiny amount of traffic on these links, so I have not tried to figure it out in more detail....

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are missing some sneaky details that Intel has not talked about. It turns out that there is a very small amount of traffic through the three edges that one would expect to be idle (the top won't be idle because of IO).

My current interpretation is that this traffic is related to rare traffic collisions between traffic shifting from the vertical links to the horizontal links.

I have never seen more than a tiny amount of traffic on these links, so I have not tried to figure it out in more detail....

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page