- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Greetings,

- Looking at the below link, what exactly is the difference between non-precise and precise monitoring? Might seem a silly question- but why would anyone ever use unprecise monitoring??

- In the below link what is the difference between a "call" and "non-call"? Would one of these refer to polymorphic virtual methods?

- In the same below link, I would like to see the value for the event "INDIRECT_NON_CALL" and I can see a mask. This appears to be some sort of bit manipulation device. How exactly do I see the value of this event counter? Where/what do I do with the mask?

In short, I am trying to work out which event counters I need to look at to observe indirect branch mispredictions for virtual calls. I am presuming I am close with these "INDIRECT" event counters?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi T C:

For precise vs non-precise, you don't always get a choice. Most events are non-precise! Case in point, the link you referenced. There may not be any precise equivalent events available from the performance monitoring unit of the processor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MrAnderson (Intel) wrote:

Hi T C:

For precise vs non-precise, you don't always get a choice. Most events are non-precise! Case in point, the link you referenced. There may not be any precise equivalent events available from the performance monitoring unit of the processor.

Hi- thanks for that. Don't suppose you have any insight in to the other 2 questions?

Thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As far as I was able to understand NON_CALL could be related to branch to the target which does not contain any function call.

DIRECT_NEAR_CALL could mean branch to the target in the same segment and execution of the call instruction.

Machine code level and underlying CPU microarchitecture probably does not "understand" virtual functions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

>>>In the same below link, I would like to see the value for the event "INDIRECT_NON_CALL" >>>

Usually virtual function will be called indirectly through the pointer.So in this case of virtual function call I would suggest to measure INDIRECT_NEAR_CALL.

In assembly it should like this:

call dword ptr [eax] ; eax contains a pointer to VTBL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

iliyapolak wrote:

>>>In the same below link, I would like to see the value for the event "INDIRECT_NON_CALL" >>>

Usually virtual function will be called indirectly through the pointer.So in this case of virtual function call I would suggest to measure INDIRECT_NEAR_CALL.

In assembly it should like this:

call dword ptr [eax] ; eax contains a pointer to VTBL

So how do I use these "masks" to see the additional event counters?

I wish intel would just show all of the raw columns in the GUI!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

T C wrote:

Quote:

iliyapolak wrote:>>>In the same below link, I would like to see the value for the event "INDIRECT_NON_CALL" >>>

Usually virtual function will be called indirectly through the pointer.So in this case of virtual function call I would suggest to measure INDIRECT_NEAR_CALL.

In assembly it should like this:

call dword ptr [eax] ; eax contains a pointer to VTBL

So how do I use these "masks" to see the additional event counters?

I wish intel would just show all of the raw columns in the GUI!

If I am not wrong those events should have corresponding MSR registers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@T C, instead of making you program masks, we typically enumerate the counters, e.g., MEM_LOAD_UOPS_LLC_HIT_RETIRED

- MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HIT

- MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HIT_PS

- MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HITM

- MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HITM_PS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MrAnderson (Intel) wrote:

@T C, instead of making you program masks, we typically enumerate the counters, e.g., MEM_LOAD_UOPS_LLC_HIT_RETIRED

- MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HIT

- MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HIT_PS

- MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HITM

- MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HITM_PS

Hi, what do you mean by this exactly?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@T C, you said, "So how do I use these "masks" to see the additional event counters?" You don't need to use masks, the additional counters are enumerated in the VTune Amplifier XE tool. Unless I am totally missing your point?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MrAnderson (Intel) wrote:

@T C, you said, "So how do I use these "masks" to see the additional event counters?" You don't need to use masks, the additional counters are enumerated in the VTune Amplifier XE tool. Unless I am totally missing your point?

Could you please explain what you mean by "enumerated"?

I have an event counter called MEM_LOAD_UOPS_LLC_HIT_RETIRED and it has a value. Other than that I have no idea how I need to get the various "subset" counters- except you tell me they are enumerated?

Enumerated just means things are listed one by one- hence ive no idea how this applies in this context.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Right, so if you want the XSNP_HIT sub-counter, the SDM says it has a mask value of '2'. Only, you don't have to know that or use it, because VTune Amplifier XE allows you to select MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HIT.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MrAnderson (Intel) wrote:

Right, so if you want the XSNP_HIT sub-counter, the SDM says it has a mask value of '2'. Only, you don't have to know that or use it, because VTune Amplifier XE allows you to select MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_HIT.

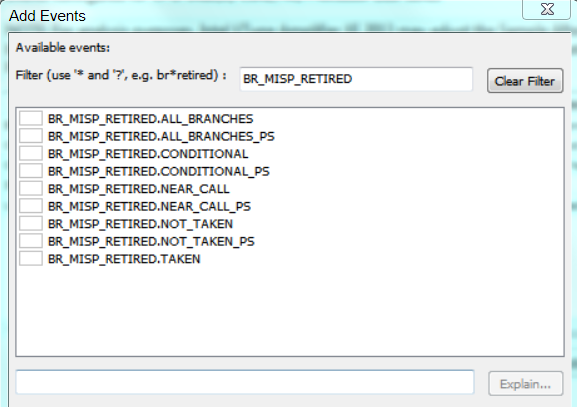

Massive apologies- I now understand why you were confused when I asked what did you mean. Yes for that particular example they are "enumerated", ie they are all on display. However, let us take BR_MISP_RETIRED:

I only have BR_MISP_RETIRED.ALL_BRANCHES_PS. I do not have any of the other enumerated options in my VTune results.....

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page