- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

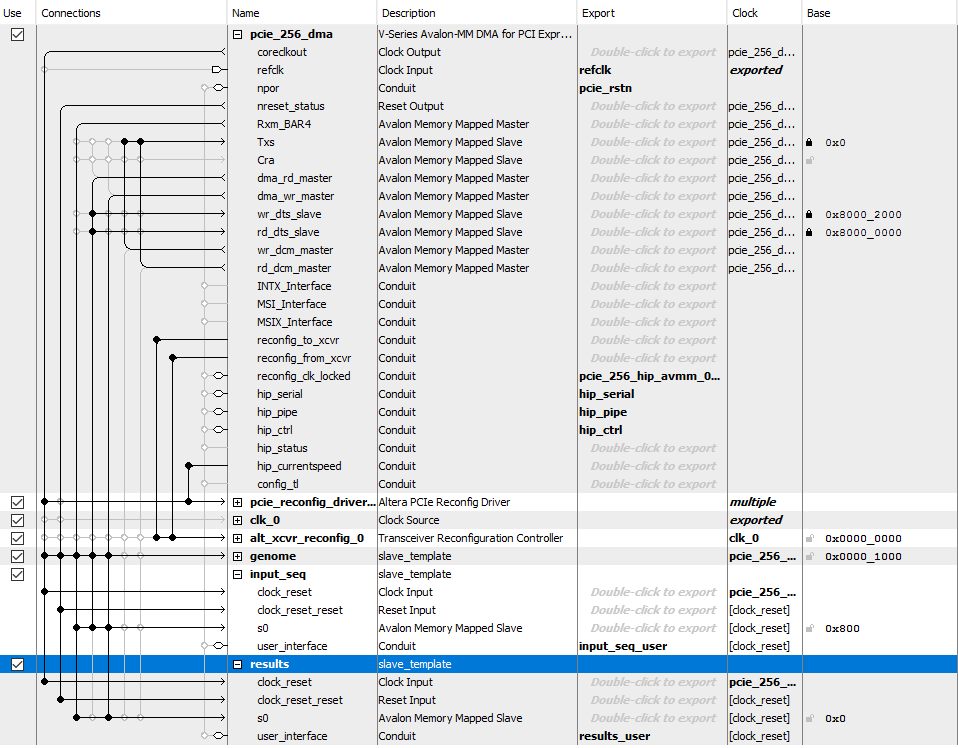

I am trying to transfer data from a PC to a FIFO on the FPGA. I am using PCIE DMA for the transfer. That data is then used in calculations, and the results are stored in another FIFO that then has to be read form the PC. I am experimenting with several setups but none of them have worked so far:

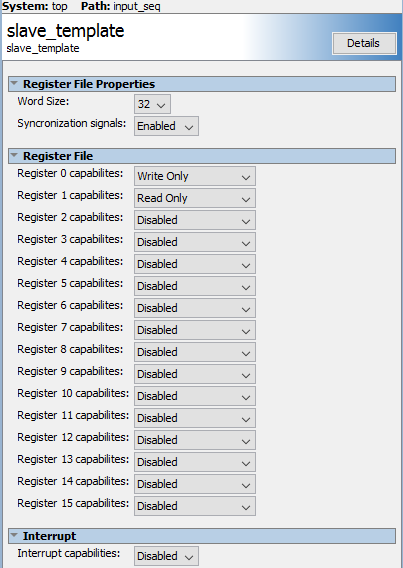

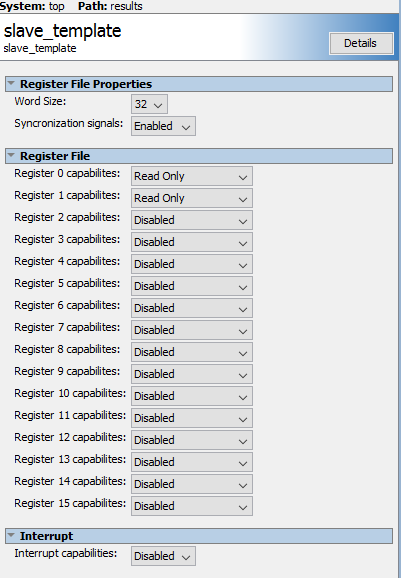

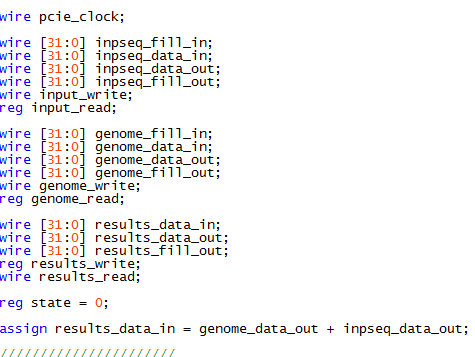

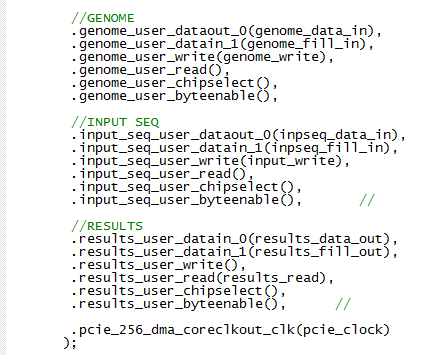

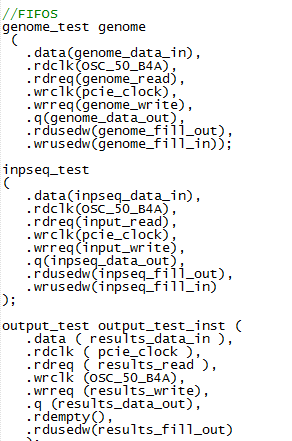

(1)Use instances of the avalon slave template in the platform designer, connect them to the PCIE DMA, and export the user signals to FIFOs inside my verilog modes.

(2)Use an Avalon MM FIFO in the platform designer connect it to instantces of the Avalon master template, and export the conduits of those templates to the part in my verilog code that needs to communicate with the FIFOs.

(3)If all else fails I might try using PIOs.

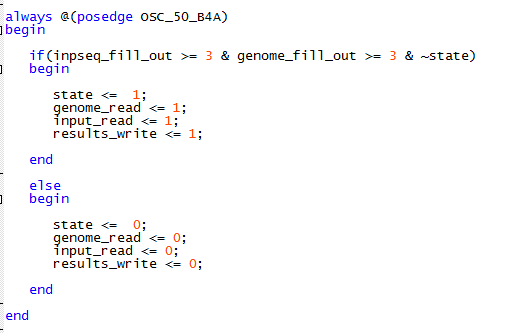

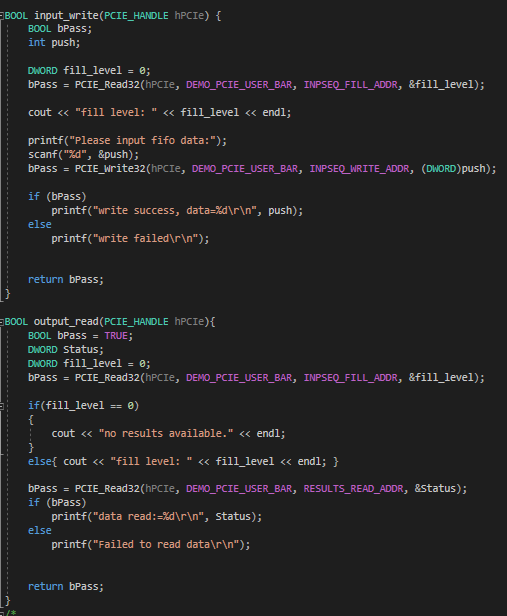

Insight on whether one or none of these methods is correct would be appreciated. But my question here is about method 1. I created a test to see if I could get it to work, but it doesn't and I would appreciate Insight on to why it doesn't, if it's at all doable and how, if it is. The test consists of writing integers to two FIFOs. As long as they are above a certain fill level, they are both read, their outputs added, and written to a third FIFO which should be readable from the PC. No matter what I do, the fill levels(whatever variable I am actually reading at least) of all 3 FIFOs stay at 0, and 0 is all I can read ot of the output FIFO. Here are screenshots of the system:

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hie,

Could you provide more details as following so I can check if you could directly use Intel's IP generated reference design to transfer data

i. Which FPGA device

ii. Quartus version used

Regards,

Nathan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have solved the issue by writing a custom component with a custom avalon slave.