- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sir/ madam

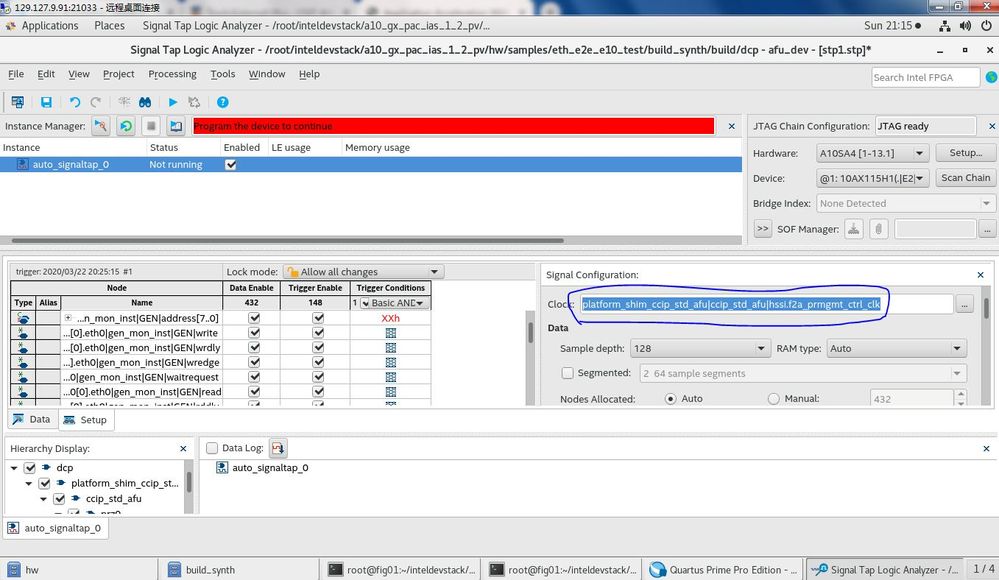

I am trying to put a signap file into ethe_e2e_e10 project.

I follow the design guideline about how to install a signaltap in chapter 6 of AFU design user guide.

I can see my stp file be involved during the compilation

but I had a error like below

auto_signaltap_auto_signaltap_0.clock must be connected to a clock output.

I use platform_shim_ccip_std_afu|ccip_std_afu|hssi.f2a_prmgmt_ctrl_clk as a sample clock in signaltap. but seems not working.

Can you give me some suggestion about this?

thanks

Jim

Error (11176): M_alt_sld_fab_0.alt_sld_fab_0: add_instance: Can't create component type altera_sld_agent_endpoint_tieoff

Info (11172): invoked from within

Info (11172): "add_instance sldfabric_t0 altera_sld_agent_endpoint_tieoff"

Info (11172): ("eval" body line 32)

Info (11172): invoked from within

Info (11172): "eval $tcl"

Info (11172): (procedure "compose" line 36)

Info (11172): invoked from within

Info (11172): "compose"

Info (11172): invoked from within

Info (11172): "interp eval $slave {

Info (11172): Compose

Info (11172): }"

Error (11176): M_alt_sld_fab_0.alt_sld_fab_0.alt_sld_fab_0.auto_signaltap_auto_signaltap_0.clock: auto_signaltap_auto_signaltap_0.clock must be connected to a clock output

Error (11176): Error opening /root/inteldevstack/a10_gx_pac_ias_1_2_pv/hw/samples/eth_e2e_e10_test/build_synth/build/qdb/_compiler/afu_synth/root_partition/17.1.1/partitioned/1/.cache/sld_fabrics/ipgen/alt_sld_fab_0/alt_sld_fab_0.ip.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sir/Madam,

I Have noticed there is a document AN 845: Signal Tap Tutorial for Intel ® Arria ® 10 Partial Reconfiguration Design.

That document asked user need to install SLD JTAG Bridge Agent in the static region, and Install the SLD JTAG Bridge Host in the PR region of the several revisions including default persona, debugging persona.

Because PAC design flow is PR flow, so I think the SLD JTAG Bridge Agent has been installed in the static region which is encrypted and user cannot touch and modify.

And for AFU PR region, user needs to install the SLD JTAG Bridge Host in the green_bs top level. Is that correct?

I go back to check another example project nlb_mode_0_stp, and checked the top module of green_bs, and found below code, seems they are relating to JTAG,

module green_bs

(

// CCI-P Interface

input logic Clk_400, // Core clock. CCI interface is synchronous to this clock.

input logic Clk_200, // Core clock. CCI interface is synchronous to this clock.

input logic Clk_100, // Core clock. CCI interface is synchronous to this clock.

input logic uClk_usr,

input logic uClk_usrDiv2,

input logic SoftReset, // CCI interface reset. The Accelerator IP must use this Reset. ACTIVE HIGH

input logic [1:0] pck_cp2af_pwrState,

input logic pck_cp2af_error,

output logic [CCIP_TXPORT_WIDTH-1:0] bus_ccip_Tx, // CCI-P TX port

input logic [CCIP_RXPORT_WIDTH-1:0] bus_ccip_Rx, // CCI-P RX port

`ifdef INCLUDE_DDR4

input logic DDR4a_USERCLK,

input logic DDR4a_waitrequest,

input logic [511:0] DDR4a_readdata,

input logic DDR4a_readdatavalid,

output logic [6:0] DDR4a_burstcount,

output logic [511:0] DDR4a_writedata,

output logic [26:0] DDR4a_address,

output logic DDR4a_write,

output logic DDR4a_read,

output logic [63:0] DDR4a_byteenable,

input logic DDR4b_USERCLK,

input logic DDR4b_waitrequest,

input logic [511:0] DDR4b_readdata,

input logic DDR4b_readdatavalid,

output logic [6:0] DDR4b_burstcount,

output logic [511:0] DDR4b_writedata,

output logic [26:0] DDR4b_address,

output logic DDR4b_write,

output logic DDR4b_read,

output logic [63:0] DDR4b_byteenable,

`endif

`ifdef INCLUDE_ETHERNET

pr_hssi_if.to_fiu hssi,

`endif // INCLUDE_ETHERNET

// JTAG Interface for PR region debug

input logic sr2pr_tms,

input logic sr2pr_tdi,

output logic pr2sr_tdo,

input logic sr2pr_tck,

input logic sr2pr_tckena

);

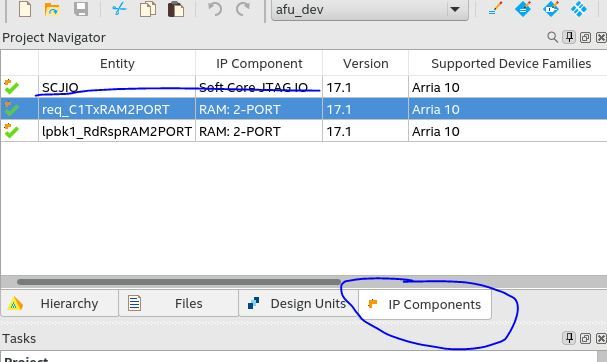

but not sure. Because above code in red color are not same as the example code mentioned in document AN 845. Also from the nlb_mode_0_stp project GUI,I cannot find the SLD JTAG Bridge Host IP core showing up in the IP section under the project navigator view as below, but nlb_mode_0_stp definitely can support a working signaltp I have confirmed.

Can you please give me some suggestion about that ?

How do I enable my own signaltap in PR flow and how to understand above question?

I am working on enabling stp on eth_e2e_e10 example? If you have a stp enabled project, can you share it with me?

Many thanks

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please close this service request since I have solved the issue, thanks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page