- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sir?Madam

I am running the eth_e2e_e10 design example now.

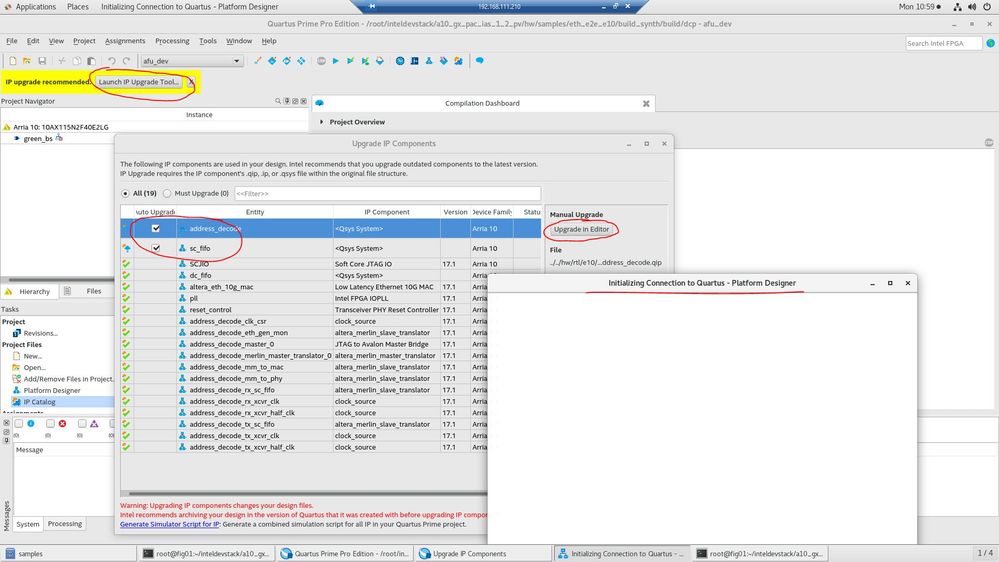

I have a IP upgrading issue now .

When I open the Quartus pro GUI in linux, and open the dcd.qpf project , system reminder to upgrade several IP core, I can click button Launch IP upgrade Tools, and seems several IP cores be upgrade successfully except address_decide and sc_fifo, seems that processing must be done through platform designer, which fails to show up correctly.

May I know which part of design based on platform designer?

Because I can not lautch platform designer gui correctly, any steps I can take to solve this issue?

I guess the issue might be caught by JAVA, so I print java version here for reference.

thanks

Jim

[root@fig01 a10_gx_pac_ias_1_2_pv]# uname -a

Linux fig01 3.10.0-957.10.1.el7.x86_64 #1 SMP Mon Mar 18 15:06:45 UTC 2019 x86_64 x86_64 x86_64 GNU/Linux

[root@fig01 a10_gx_pac_ias_1_2_pv]# java -version

openjdk version "1.8.0_201"

OpenJDK Runtime Environment (build 1.8.0_201-b09)

OpenJDK 64-Bit Server VM (build 25.201-b09, mixed mode)

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Some update , when I click the button Auto upgrade,Quartus printed below error information,any other way I can use to upgrade these IP if I can not open the qsys platform designer? thanks

Error: 2020.03.16.11:11:48 Error: Generation for Standard System (.qsys) files is not available in Pro, you can upgrade these files to Pro by opening them in Platform Designer for Quartus Pro.

Error: Quartus Prime Shell was unsuccessful. 15 errors, 0 warnings

Error: Peak virtual memory: 822 megabytes

Error: Processing ended: Mon Mar 16 11:12:26 2020

Error: Elapsed time: 00:00:50

Error: Total CPU time (on all processors): 00:02:00

Error(14923): Error upgrading Platform Designer file "../../hw/rtl/e10/fifo_scfifo/sc_fifo.qsys"

Error: 2020.03.16.11:12:14 Error: address_decode.rx_xcvr_half_clk.clk_in: rx_xcvr_half_clk.clk_in must be connected to a clock output

Error: 2020.03.16.11:12:14 Error: address_decode.rx_xcvr_half_clk.clk_in_reset: rx_xcvr_half_clk.clk_in_reset must be connected to a reset source

Error: 2020.03.16.11:12:14 Error: qsys-generate failed with exit code 3: 2 Errors, 0 Warnings

Error: 2020.03.16.11:12:16 Error: address_decode.rx_xcvr_half_clk.clk_in: rx_xcvr_half_clk.clk_in must be connected to a clock output

Error: 2020.03.16.11:12:16 Error: address_decode.rx_xcvr_half_clk.clk_in_reset: rx_xcvr_half_clk.clk_in_reset must be connected to a reset source

Error: 2020.03.16.11:12:16 Error: qsys-generate failed with exit code 3: 2 Errors, 0 Warnings

Error: 2020.03.16.11:12:17 Error: address_decode.rx_xcvr_half_clk.clk_in: rx_xcvr_half_clk.clk_in must be connected to a clock output

Error: 2020.03.16.11:12:17 Error: address_decode.rx_xcvr_half_clk.clk_in_reset: rx_xcvr_half_clk.clk_in_reset must be connected to a reset source

Error: 2020.03.16.11:12:17 Error: qsys-generate failed with exit code 3: 2 Errors, 0 Warnings

Error(14923): Error upgrading Platform Designer file "../../hw/rtl/e10/address_decoder/address_decode.qsys"

Error(11133): IP component QsysPrimePro with file "../../hw/rtl/e10/fifo_scfifo/sc_fifo.qsys" upgrade failed

Error(11133): IP component QsysPrimePro with file "../../hw/rtl/e10/address_decoder/address_decode.qsys" upgrade failed

Error(23031): Evaluation of Tcl script /root/inteldevstack/intelFPGA_pro/quartus/common/tcl/internal/ip_regen/ip_regen.tcl unsuccessful

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may use the command line method to upgrade the qsys system without using the GUI

qsys-generate <IP variation file>.qsys

The IP upgrade option is available in Table 172. Command-Line Options for qsys-generate https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-platform-designer.pdf

Do you see any error messages when you launch the GUI?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY

thanks for your suggestion.

based on the error information from GUI when I was upgrading IP before , I knew 2 ip need to be upgrade manually.

Error: 2020.03.16.11:11:48 Error: Generation for Standard System (.qsys) files is not available in Pro, you can upgrade these files to Pro by opening them in Platform Designer for Quartus Pro.

Error: Quartus Prime Shell was unsuccessful. 15 errors, 0 warnings

Error: Peak virtual memory: 822 megabytes

Error: Processing ended: Mon Mar 16 11:12:26 2020

Error: Elapsed time: 00:00:50

Error: Total CPU time (on all processors): 00:02:00

Error(14923): Error upgrading Platform Designer file "../../hw/rtl/e10/fifo_scfifo/sc_fifo.qsys"

Error: 2020.03.16.11:12:14 Error: address_decode.rx_xcvr_half_clk.clk_in: rx_xcvr_half_clk.clk_in must be connected to a clock output

Error: 2020.03.16.11:12:14 Error: address_decode.rx_xcvr_half_clk.clk_in_reset: rx_xcvr_half_clk.clk_in_reset must be connected to a reset source

Error: 2020.03.16.11:12:14 Error: qsys-generate failed with exit code 3: 2 Errors, 0 Warnings

Error: 2020.03.16.11:12:16 Error: address_decode.rx_xcvr_half_clk.clk_in: rx_xcvr_half_clk.clk_in must be connected to a clock output

Error: 2020.03.16.11:12:16 Error: address_decode.rx_xcvr_half_clk.clk_in_reset: rx_xcvr_half_clk.clk_in_reset must be connected to a reset source

Error: 2020.03.16.11:12:16 Error: qsys-generate failed with exit code 3: 2 Errors, 0 Warnings

Error: 2020.03.16.11:12:17 Error: address_decode.rx_xcvr_half_clk.clk_in: rx_xcvr_half_clk.clk_in must be connected to a clock output

Error: 2020.03.16.11:12:17 Error: address_decode.rx_xcvr_half_clk.clk_in_reset: rx_xcvr_half_clk.clk_in_reset must be connected to a reset source

Error: 2020.03.16.11:12:17 Error: qsys-generate failed with exit code 3: 2 Errors, 0 Warnings

Error(14923): Error upgrading Platform Designer file "../../hw/rtl/e10/address_decoder/address_decode.qsys"

Error(11133): IP component QsysPrimePro with file "../../hw/rtl/e10/fifo_scfifo/sc_fifo.qsys" upgrade failed

Error(11133): IP component QsysPrimePro with file "../../hw/rtl/e10/address_decoder/address_decode.qsys" upgrade failed

Error(23031): Evaluation of Tcl script /root/inteldevstack/intelFPGA_pro/quartus/common/tcl/internal/ip_regen/ip_regen.tcl unsuccessful

So I close quartus GUI and did below

[root@fig01 e10]# pwd

/root/inteldevstack/a10_gx_pac_ias_1_2_pv/hw/samples/eth_e2e_e10/hw/rtl/e10

[root@fig01 e10]# cd address_decoder/

[root@fig01 address_decoder]# qsys-generate address_decode.qsys

bash: qsys-generate: command not found...

[root@fig01 address_decoder]#

seems command is not found for Intel PAC card OPAE design environment.

any other steps I can try for the platform designer GUI not showing correctly?that is part of design tolls ,which might be used in further development.

thanks

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

also I think the upgrading failed issue might be caused by the connections related to module rx_xcvr_half_clk from the printed error information.

it was not only about upgrade flow, but also design itself. this is the vendor provided design example ,I did not modify anything.

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

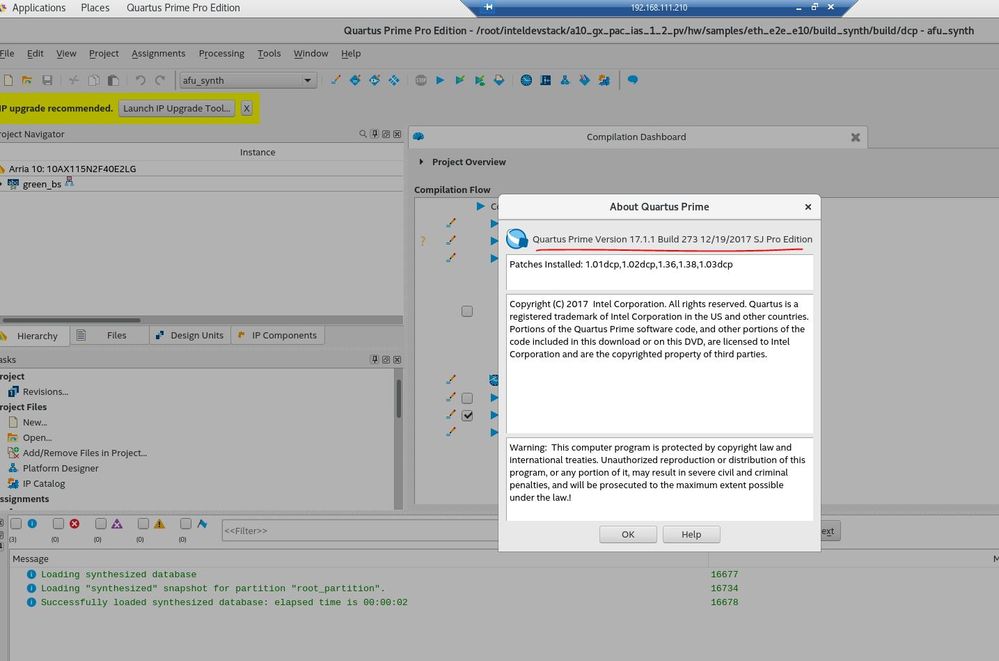

May I know which Quartus prime software edition and version is using?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MeiYanL

thanks for your feedback.

I am using Quartus Prime Pro 17.1.1 build 273,which is recommended version by the Intel PAC user manual.

Best regard

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sir/madam,

Based on my recent feedback, can I have some suggestion to solve this platform designer GUI issue and IP upgrading issue?

thanks

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I had build the design example and I am able to open the platform designer to upgrade the IP component.

As mentioned earlier, the platform designer is hang on initializing page, you may need to follow the instruction as below:

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/tools/2017/why-does-qsys-pro-hang-at-initializing-qsysipc-bridge.html

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MeiYanL,

Thanks for your effort.

I have tried that solution, platform designer was hanging and had no response to clicking of close windows button. Even I quite the Quartus ,platform designer was still there. I had to restart server to kill it.

May I know your Quartus version?

Have a good weekend

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

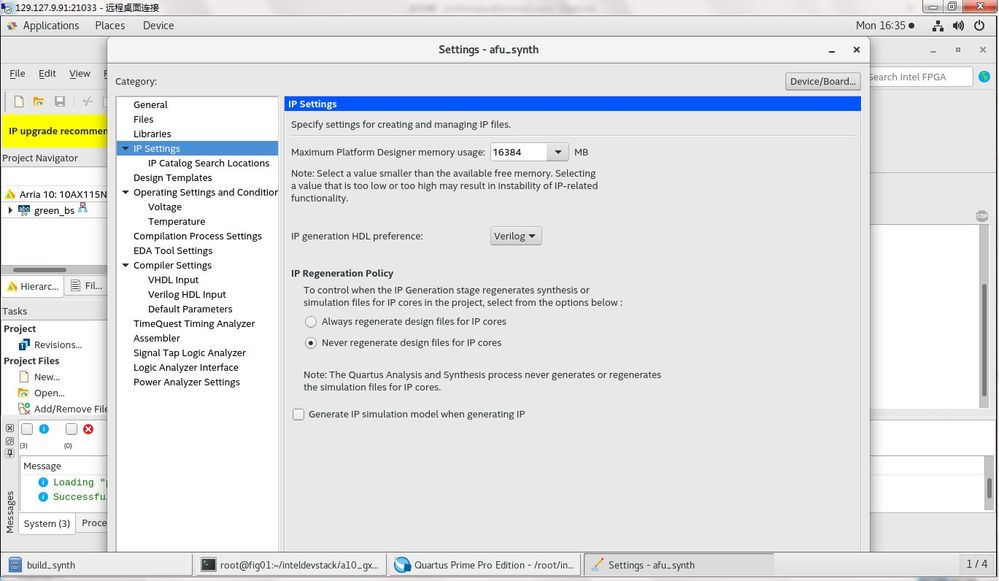

I tested on the Quartus Prime Pro v17.1.1 software as recommended in the document.

According to https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/tools/2017/why-does-qsys-pro-hang-at-initializing-qsysipc-bridge.html, it might be cause by machine load.

You may need to try go to the Quartus menu: Assignments > Settings, then on the left panel select the IP Settings and on the right panel set the "Maximum Platform Designer memory usage" to the max value.

For you information, you could use the task manager to close the Platform Designer UI.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MeiYanL,

thanks for your suggestion.

I have tried to maximum the memory usage, but can't click ok button since it is not visible and the setting windows is not able to zoo in or zoo out.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may need to try the method as below:

1. Resize the monitor with different scale and layout as step below:

-Right-click an empty spot on the desktop.

-Click Personalize.

-Click Display Settings.

-Note the current setting of the "Change size of..." and "Resolution".

-Choose the size and resolution to 1920x1080.

-If the screen looks OK, click "Yes" to keep these display settings.

2. Resize Quartus Prime software front setting as steps below:

-open Quartus Prime software

-click Tools>Options>General>Fonts

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MeiYanL,

thanks for your feedback.

My graphic card on clinet computer(working from home) supports resolution up to 1440*900 .

with that settings seems not big enough to fit part of Quartus window.

Can I get you compiled project ?

Best regard

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

After update the IP files, I had compile the project file. But there is some error on my side.

I will need some time to investigate for it.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MeiYanL,

thanks for your support, have a good weekend.

Jim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page