- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

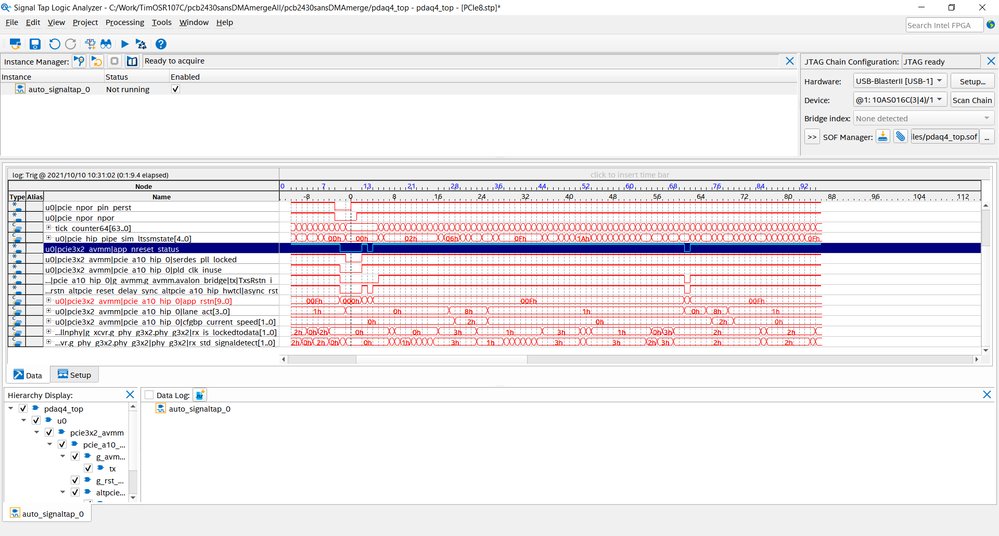

As shown in SigTap snapshot below, there is an extra pulse of app_nreset_status at sample 61. When this happens, the PCIe device does not enumerate correctly in Windows.

I also have a dump of raw data values for capture below if that helps.

Any ideas what could cause this extra reset to be issued?

Thanks.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know which device family you are using? Could you share the stp file?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Device is Arria10 (10AS016C4U19E3SG)

.stp and a text dump of capture is attached.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know what is the speed and link width you are trying to achieve? Could you check if the power supply (VCCR_GXB) is set correctly in the Assignment editor and measure the power supply (VCCR_GXB) supplied to FPGA board is matched with voltage set in the design setting?

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

PCIe Core mode is set to: Gen3 X2, 128bit, 125MHz

VCCR_GXB is 1.03V when measured on the board (pins J19 and J20).

I don't see where these pins (J19 and J20) are called out in the assignment editor, where are these located?

Thx.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may set the assignment using the pin planner or assignment editor

For Pin Planner

- Right-click on a blank area in the All Pins list and select Customized Columns

- Select VCCR_GXB / VCCT_GXB Voltage from Available Columns and click the> button

- Make sure it is added to the All Pins list and select the transceiver pin voltage you want to change

■ For Assignment Editor

- Register the corresponding XCVR pin name in the To field

- Select VCCR_GXB / VCCT_GXB Voltage in the Assignment Name field

- Select the voltage of the corresponding XCVR pin

From the Fault Tree Analysis (FTA) for Arria 10 PCIe Link Up Issue

https://community.intel.com/t5/FPGA-Wiki/FTA-PCI-express/ta-p/735993, I believe you are at Is rx_std_signaldetect asserted (Hypothesis 4). Can you try the suggestions in FTA_Table_View (No 4)?

If the suggestions in the FTA are not helpful, could you try to run at lower speed and see if this is a problem running at Gen3?

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if you have any updates?

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page