- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

good news:

1. I have successfully simulated design in Modelsim -> ATX PLL relocked after REFCLK is present ->o.k.

2. I have successfully downloaded design to hardware -> ATX PLL relocked after REFCLK is present ->o.k.

Thank's for your advice!

Regards

diddi1057

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

As I understand it from your PDF, you observe an issue where ATX PLL unable to achieve lock due to no refclk present at power up. You have tested recalibration but seems not helping. With stable refclk present at power up, there PLL is locked.

To facilitate further debugging, just to check with you on the following:

1. Just wonder if you have had a chance to run through simulation with your recalibration steps to see if the ATX PLL is able to re-achieve lock?

2. Can you try to hold the ATX PLL in reset during power up, release when stable refclk is present. Then perform recalibration to ATX PLL followed by a reset.

3. Just to double check if the CLKUSR is directly sourced from a free-running and stable clock source on board?

4. Please share with me further on the steps that you have taken for recalibration ie the register writing sequence. I would like to see if can spot any anomaly.

Please let me know if there is nay concern. Thank you.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

As I understand it from your PDF, you observe an issue where ATX PLL unable to achieve lock due to no refclk present at power up. You have tested recalibration but seems not helping. With stable refclk present at power up, there PLL is locked.

Yes, correct!

To facilitate further debugging, just to check with you on the following:

1. Just wonder if you have had a chance to run through simulation with your recalibration steps to see if the ATX PLL is able to re-achieve lock?

Did not make simulation yet, will try ...

2. Can you try to hold the ATX PLL in reset during power up, release when stable refclk is present. Then perform recalibration to ATX PLL followed by a reset.

Will try that.

3. Just to double check if the CLKUSR is directly sourced from a free-running and stable clock source on board?

Yes, CLKUSR is an external free running source=100MHz, verified

4. Please share with me further on the steps that you have taken for recalibration ie the register writing sequence. I would like to see if can spot any anomaly.

recalib register writing sequence: refer to pma_pll_calibration.vhd state machine.

please hold on for some time for investigation.

Please let me know if there is nay concern. Thank you.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

1. Just wonder if you have had a chance to run through simulation with your recalibration steps to see if the ATX PLL is able to re-achieve lock?

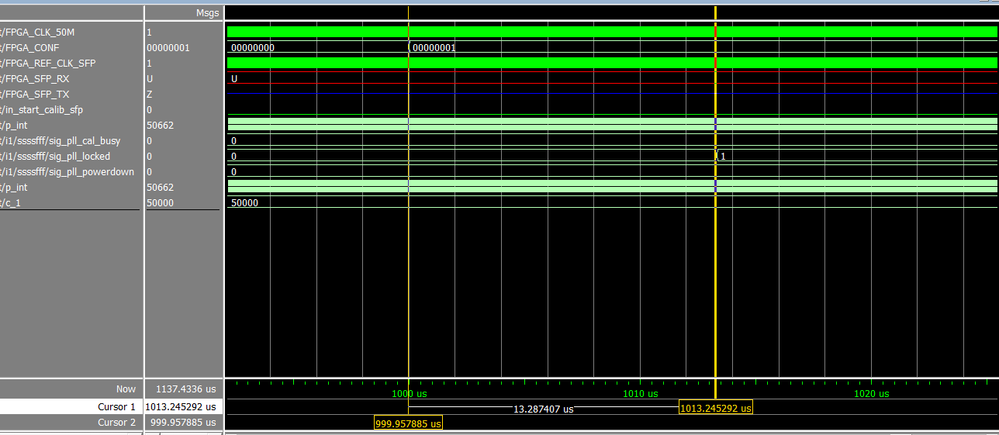

Just made simulation:

-- Disabled Refclock for 1ms at start of Simulation

-- Then enabled Refclock

-- ATX PLL achieved lock after 13 us (without recalibration process)

Simulation takes a long time(~15 minutes for 2 ms). Wonder if the ATX PLL does also lock, when Refclock is disabled for longer time period at start of simulation(e.g. seconds)

2. Can you try to hold the ATX PLL in reset during power up, release when stable refclk is present. Then perform recalibration to ATX PLL followed by a reset.

Has no effect

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Did you get my information about the simulation of the ATX PLL ?

I have no idea about whats going on there!

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Sorry for the delay. Regarding the simulation with the ATX PLL recalibration, the purpose of doing this is to check if the steps of recalibration is OK. In simulation, after ATX PLL achieves lock, if you trigger the recalibration, you should see ATX PLL going into recalibration and then out from recalibration and then achieve lock.

I am not sure if the model can replicate the no refclk behavior at power up. Thus, the purpose of simulation is to check the recalibration steps.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

performed new simulation:

REFCKL is stable at startup.

ATX PLL locked after 13 us -> OK

Then trigger recalibration: signal pll_cal_busy stays '0', signal pll_locked stays '1'

For ATX PLL recalibration, I performed the following steps (Intel® Arria® 10 Transceiver PHY

User Guide, §7.4.1.1)

1.Request access to the internal configuration bus by writing 0x2 to offset address 0x0[7:0].

2.Read-Modify-Write 0x1 to the offset address 0x100[0] of the ATX PLL.

3.Release the internal configuration bus to PreSICE to perform recalibration by writing 0x1 to offset address 0x0[7:0].

Is there any register I also have to configure for ATX PLL recalibration?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Thanks for your update. Your steps tally with those described in the user guide. I checked with register map and do not spot any anomaly. Just to check with you when you are doing the same steps in hardware, do you see the pll_cal_busy go high after triggering recalibration?

Can you share with me a simple test design with one channel Native PHY + ATX PLL + reset controller which could replicate your observation in Modelsim? I would like to further look into it.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

thanks for your answer. Will try do give you the required info next Monday!

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

attached the simple simulation project with one channel Native PHY + ATX PLL + reset controller. Please refer to atx_pll_simu.pdf inside project for instruction.

I have to check again the same steps in hardware, if pll_cal_busy go high after triggering recalibration ...

Best regards

diddi1057

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

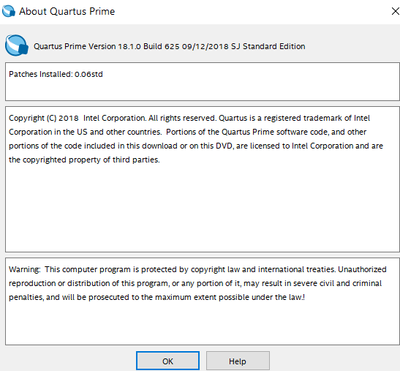

Thanks for sharing your QAR. Just to check with you which specific Quartus version that you are using? Thank you.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Would you mind to share with simulation which could be directly simulated in Modelsim ie using msim_setup.tcl without going through native link. This would be helpful to facilitate further debugging. Thank you.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

attached project using msim_setup.tcl .

Created /mentor/test_atx_pll_no_lock.do -> Adapt QSYS_SIMDIR

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Thanks for your update and sharing. I am able to run the simulation now and observe similar waveform. As I look into your transceiver_sfp.vhd, I observed that seems like you are not enabling the reconfiguration interface of the ATX PLL. Only the Native PHY reconfiguration interface is enabled and connected. To recalibrate the ATX PLL, you would need to write to the ATX PLL reconfiguration interface.

Can you try to enable the reconfiguration interface of the ATX PLL and perform the ATX PLL recalibration registers read/write process to see if it works?

Thank you.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

thanks for info! Guess thats the issue. Will try on next Monday and give you my feedback.

This was not clear in the documentation for me.

Regards

diddi1057

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Thanks for your update. Please keep me posted on the test result. Thank you.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

good news:

1. I have successfully simulated design in Modelsim -> ATX PLL relocked after REFCLK is present ->o.k.

2. I have successfully downloaded design to hardware -> ATX PLL relocked after REFCLK is present ->o.k.

Thank's for your advice!

Regards

diddi1057

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Thanks for your update. Glad to hear that you have managed to resolve the problem and get your design working.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

I believe the initial inquiry has been addressed. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.