- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am looking for dynamic reconfiguration of C10 GX fPLL.

But from the parameter editor, I was referenced to xcvr user guide.

The guide only explain the structure of the pll.

But how could I reconfigure it?

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

For confidentiality purpose the communication is taken to private conversation

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Kindly requesting to refer the below document page no: 87 for the reconfiguration

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-10/c10gx-51003.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rahul,

Thank you!

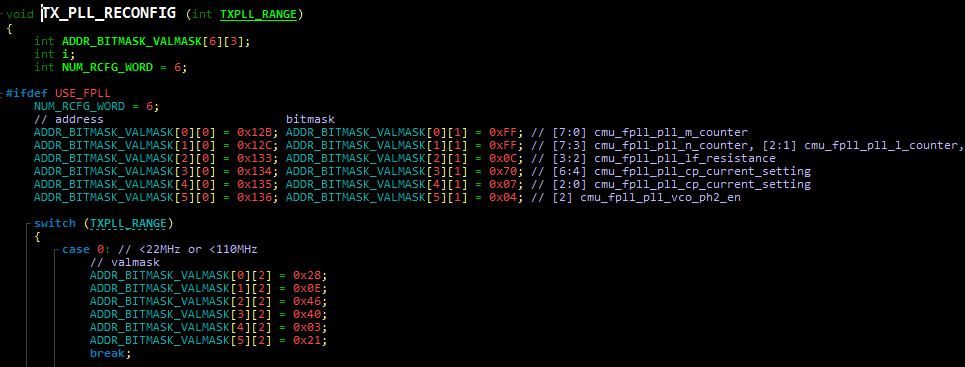

I searched the document and not able to find the register address of M/N counter..

https://www.intel.com/content/www/us/en/programmable/documentation/hki1486507600636.html

or what's the definition of register address 0x12B, 12C, 133, 134, 13 and 136....

I checked the xcvr_phy, neither..

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is it possible to follow the below application note

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an728.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rahul,

Thank you for the update.

This AN provides some useful information but can not directly mapped to FPLL.

My question is related to the C10 GX VIP reference design,

https://fpgacloud.intel.com/devstore/platform/18.0.1/Pro/cyclone-10-gx-hdmi-4kp60-with-video-and-image-processing-pipeline-reference-design/

Inside the project, we noticed the fPLL was reconfigured to different parameters by function "TX_PLL_RECONFIG'.

And we need understand and modify this function to make the product work.

Please help!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johson ,

Can you please help me to understand further on the issue , what is the issue you are facing exactly , is the reference design is not working .

Or , you could not able to change the setting on the fpll of the reference design.

The reason for the ask , is that i can contact the designer owner to solve the issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rahul,

My problem is I need to dynamically change the output settings for different resolutions.

That meas the fPLL output clock rate must following my settings. e.g. 1080p60, 1080p30, 2160p30.....

Therefore I need the know how to do that..

Unfortunately, I did not find any document reference to the fPLL register definitions nor the user guide..

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

For confidentiality purpose the communication is taken to private conversation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page