- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hello,

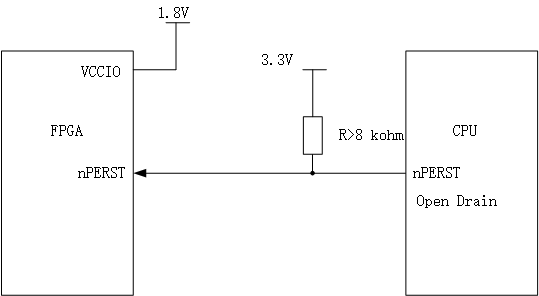

I assign IO_STANDARD 1.8 V for nPERST pin of Intel® Stratix® 10 PCI Express* Hard IP, and connect VCCIO3V to 1.8V power supply. The nPERST out from CPU is 3.3V power domain.

Bu I didn't add a 1.8V-3.3V level shifter between FPGA and CPU on nPERST by mistake.

Is there any problem with this connection?

Best Regards

Link copiado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

My understand is you compile the quartus with the nPERST pin assign to IO standard 1.8V. But in actual hardware, you supply 3.3V to the FPGA VCCIO pin which suppose need to connect with 1.8V.

This approach is not recommended and it potentially create an issue as below:

- For the FPGA IO buffer, it is using different buffer for voltage above 3V. Thus, if generate the quartus with 1.8V, it will assign a lower voltage buffer to that IO, so if you connect with higher voltage like 3.3V. It might potentially defect the IO buffer.

- this also impact the IO timing. Theoretically, nPERST pin is an reset signal and not toggle like a clock, thus timing might insignificant. But we can't predict and side effect since you connect a voltage that much more higher that what is suppose to.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Sorry i didn't describe it clearly. Following is diagram. I connect the VCCIO with 1.8V, and compile the quartus with the nPERST pin assign to IO standard 1.8V.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Ok, so the pull up resistor is connect to 3.3V. The signal is active low. I don't see any issue in term of functionality but the timing might give some side effect which we don't know the effect. Unless characterize it using hardware.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Thank you very much!

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Welcome!

- Subscrever fonte RSS

- Marcar tópico como novo

- Marcar tópico como lido

- Flutuar este Tópico para o utilizador atual

- Marcador

- Subscrever

- Página amigável para impressora