- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I generated a decimator using FIR II IP in Quartus Prime Pro 19.3.

Simulation is OK using Modelsim.

However when I include the FIR II IP in my project and click "Start Analysis & Elaboration" in Quartus 19.3, some error occurs :

Instance "xxxxxxxxxxx|xxxx.hpfircore_core" instantiates undefined entity "xxxxxxxx_rtl_core"

It's a bit like the error in the following page,

Any suggestions ?

- Tags:

- FIR

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you observe some compilation issue with FIR II IP in Q19.3Pro. For your information, I have created a simple test design with FIR II IP (Decimator) and able to pass the Q19.4Pro compilation. Note that I only have Q19.4Pro installed in my PC.

Attached is the QAR for your reference.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just to follow up with you on this. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, thanks for the following up. The problem remain unsolved.

Sorry that I should have described my problem more clearly.

My situation is that my original project has two FIR IPs, one for Low pass filter and one for decimator.

This project can be synthesized, fit, place & route successfully.

And the function works fine.

When I want to add one more decimator to this project, or more FIRs into this project.

Some error occurs during Analysis and Elaboration.

Like:

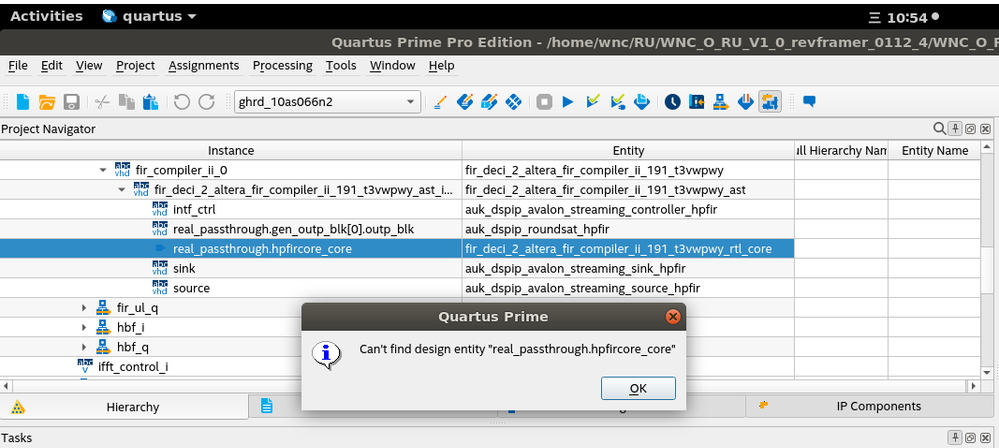

Instance "dl_data_top|dl_data_path_ant1|dl_rf_intf|fir_ul_q|fir_compiler_ii_0|fir_deci_2_altera_fir_compiler_ii_191_t3vwpwy_ast_inst|real_passthrough.hpfircore_core" instantiates undefined entity "fir_deci_2_altera_fir_compiler_ii_191_t3vwpwy_rtl_core"

If I click the Hierarchy, then it did show Can't find design entity "real_passthrough.hpfircore_core"

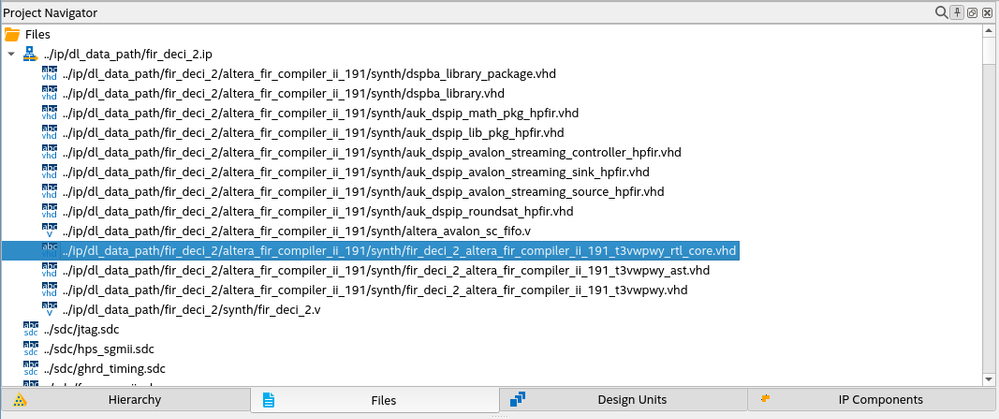

But when I click the File, the file "fir_deci_2_altera_fir_compiler_ii_191_t3vwpwy_rtl_core.vhd" does exist

Not sure if this issue related to

Why Analysis and Synthesis fails when using multiple variation of same DSP IP core

or

Quartus Compilation Fails in Quartus Prime Pro For Designs with Multiple SerialLite III IP Core Instances

The error message is similar to the multiple SerialLite III IP Core.

Thanks for answering.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

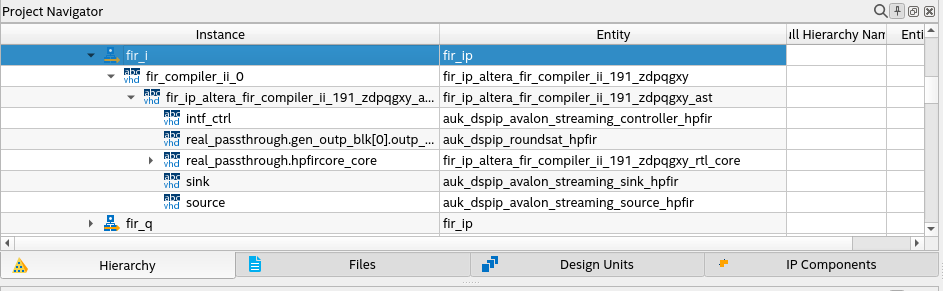

Just offering some additional snapshot for comparison.

Here is the FIR IP in the original project which can be synthesised, where the "real_passthrough.hpfircore_core" in this FIR IP is defined.

When I add new FIR IP, error message occurs as the previous post.

And the "real_passthrough.hpfircore_core" in the new FIR IP is undefined.

Not sure if I need additional setting for IPs.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. For your information, I have created simple test design with 3 FIR decimators. 2 are instantiated from the same HDL files. 1 is with different HDL files. Seems like there is no issue running the compilation till Fitter. I am using Q19.4Pro and S10 devices as these are currently available in my local PC.

You may refer to see if can spot any anomaly with yours. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just to follow up with you on this. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, it has been some time since I last heard from you. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page