- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi community member

We'd like to use DP Rx IP as eDP Rx and generate stable recover clock by bitec_clkrec module.

We already implemented it into Arria V (5AGXMB3G4F31I3N) which was referred example design in altera_dp of Quartus 17.1 and worked fine on our board and Intel evaluation board.

However, when we change pixel clock frequency of DP source (Not link rate), it didn't work fine on our board and Intel evaluation board.

We already investigate and suspect that pll reconfiguration loop in bitec_clkrec can not generate stable clock via pll reconfiguration logic by pll.

How do we investigate route cause ?

Also, we suspect initial pll parameters. Especially, bandwidth setting, charge pump setting and VIC range.

How do we consider them and decide suitable parameters ?

[Note]

Some range of recovered clock work fine.

But, other range of recovered clock don't work fine.

Best regards,

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

Is the PLL integrate in the example design or you generate it externally?

If it is integrate in the example design, I don't think it is recommend to change the frequency.

If it is generate externally, I will suggest you to refer to PLL user guide to determine the parameters.

Also, refer to Arria V Errata sheet to check it there a known issue that impact PLL with certain frequency range.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi BCT_Intel

Thank you for your reply.

My design is based on example design.

So, it is integrate in the example design.

What do you mean "change the frequency" ?

Because bitec_clkrec module generates pixel clock as recover clock from rx_ss_clk as reference clock.

If you mean that you don't recommend to change the frequency after finishing sof alignment, it is hard to track clock frequency via Mvid, HTOTAL and rdusedw on DCFIFO.

Also, I confirmed Arria V Eratta sheet.

But I could not find my device (5AGXMB3G4F31I3N) in this table.

I already heard the die revision of this device is D version.

Is this device already fixed ?

Thanks a lot,

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

The example design is provided AS-IS basis, it is not recommend to make any modification to it.

Based on the errata sheet, rev D is fixed. Can you share more on how you observe the clock is unstable?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi BCT_Intel

Thank you for your reply.

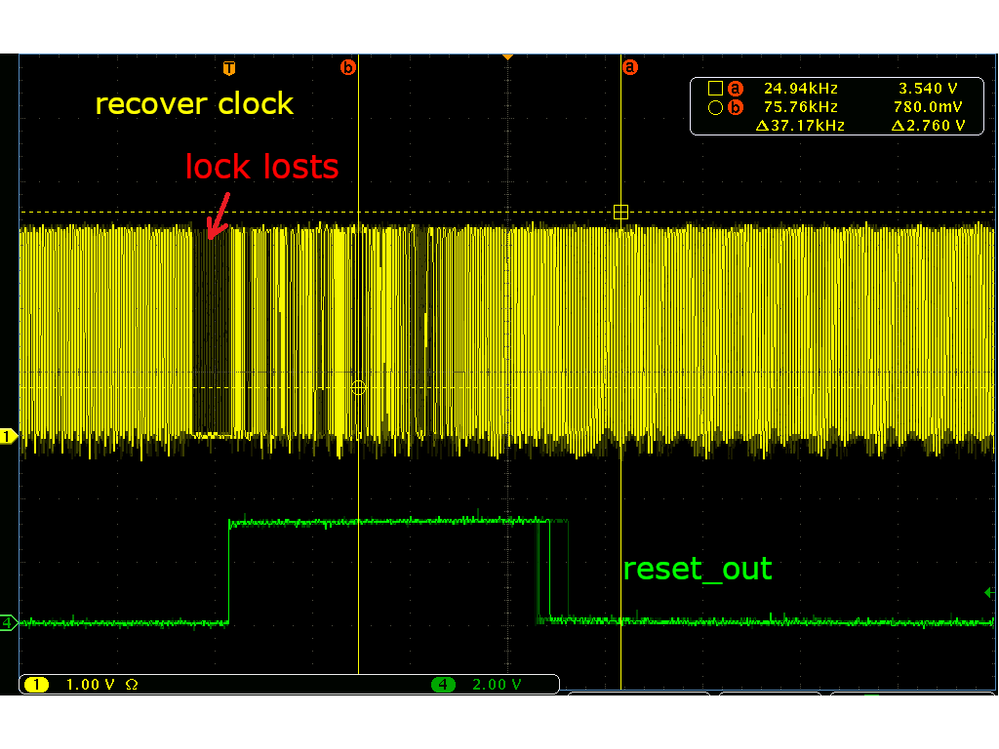

This picture is waveform around pll lock lost.

Also we already confirmed lock status on fractional PLL and this level is low when recover clock was low.

BTW, we already observed some signals which was measured by signal tap.

I'd like to share them to explain more detail. But I don't prefer here.

[Note]

Recover clock frequency is around 93.2[MHz].

Best regards,

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page