- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I was hoping someone on the forum could shed some light on a problem I have having.

I have an Arria V design with a reconfigurable integer pll. I can successfully change the frequencies of all the clocks generated from the pll. However, I am trying to change the phase of the clocks using the dynamic phase shifting. Unfortunately, I am unable to see any change of phase for any of the output clocks. I have been unable to find anything in the online documentation that says if integer plls on Arria V devices support dynamic phase shifting. This application note mainly mentions fractional plls except for mentioning the fPLLs support integer plls. https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an661.pdf I need to use an integer pll to drive the LVDS IP so changing to a fractional pll is not an option.

Any help would be much appreciated.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R_Intel,

I am happy to report I finally managed to show the dynamic phase shifting working with my integer pll design. I changed my setup so I had three identical clocks coming out of my pll. On the scope, I triggered on the first clock and changed the phase of the other two clocks. I was able to easily see the change of phase after this. I took your suggestion on board of using values of 90 and 180 degrees to start. However, using a shift counter value of one repeatedly allowed me to see the clock phase changing.

I am going to close of this issue now. Thanks again for your help!!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

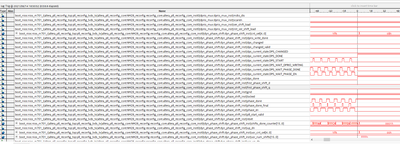

I wanted to add this Signaltap screen shot of the phase command being carried out successfully in the reconfiguration core. However, no phase changes. So I am unsure what I have done wrong. I have tried single counter changes (ie C0) and all counter changes with varying shift values and no phase change.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

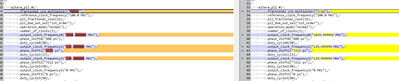

After doing a quick diff of the integer version of my pll versus a fractional version. I noticed that the diff shows no Vco is enabled in my integer pll. So I am guessing that this could possibly be the reason why the dynamic phase shifting isn't working for me. In the description of dynamic phase shifting in AN661 (page 13) the Vco is mentioned in the process. So I guess this could be the reason no dynamic phase shifting is working for me.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry I meant to say in the above post there is no Vco multiplier in my integer pll so this is possibly the reason why dynamic phase shifting is not working.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the details provided. While selecting integer PLL, the dynamic phase shift is not greyed out. So, it should be working.

AN 661 mentions that "The resolution of phase shift is a function of VCO frequency, with the smallest incremental step equal to 1/8th of the VCO period."

As, the difference between fpll and int pll is the resolutions of the output clocks, it may be cause the issue.

Could you please try doing phase shift of a bigger value, like 90 deg (1/4) or 180 deg (1/2)?

Also, can you try out, just for experiment, same design with fpll?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R_Intel,

thank you for replying to my query. I will try your suggestion of changing the phase shift values relative to 90 and 180 degrees. If that does not work I will try the fpll design instead of the integer pll I am currently using.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R_Intel,

I am happy to report I finally managed to show the dynamic phase shifting working with my integer pll design. I changed my setup so I had three identical clocks coming out of my pll. On the scope, I triggered on the first clock and changed the phase of the other two clocks. I was able to easily see the change of phase after this. I took your suggestion on board of using values of 90 and 180 degrees to start. However, using a shift counter value of one repeatedly allowed me to see the clock phase changing.

I am going to close of this issue now. Thanks again for your help!!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page