- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi guys,

I am trying to compile the Example Design for Multichannel DMA PCIe IPCore. However the fitter plan stage failed and the following error has been reported.

The issue appeared when I initially choose the partnumber 1SG040HH3F35E3VG.

On the other hand I can successfully compiled the same project with 1SG065HH3F35E3VG partnumber, which is pin to pin compatible.

Error message:

Info(175028): The pin name(s): pcie_rstn_pin_perst

Error(175006): There is no routing connectivity between the pin and destination HSSI_CR2_PHIP2_CORE

Info(175027): Destination: HSSI_CR2_PHIP2_CORE dut|dut|hip|altera_pcie_s10_hip_ast_pipen1b_inst|wys

Error(175022): The pin could not be placed in any location to satisfy its connectivity requirements

Info(175021): The HSSI_CR2_PHIP2_CORE was placed in location HSSICR2PHIP2CORE_5TL0

Please find attached the two arquives project for 1SG040HH3F35E3VG and 1SG065HH3F35E3VG.

Regards

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Arley,

We do not receive any response from you to the previous answer that I provided.

Also, I strongly believe that my previous answer had solve your problem (Please correct me if I am wrong)

Hence, This thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Otherwise, the community users will continue to help you on this thread. Thank you

If you feel your support experience was less than a 9 or 10,

please allow me to correct it before closing or let me know the cause so that I may improve your future support experience.

Regards,

Wincent_Intel

Link kopiert

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi,

Same question been ask in

Do you need me to support you here or at the previous one ?

I shall close either one a duplicate.

Let me know if you have any other idea.

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi,

Please allow me to have sometime to look at the .qar file.

Get back to you soon as possible.

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

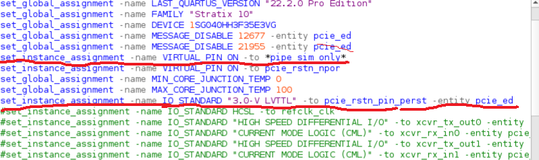

Hi Arley,

Can you try to

set_instance_assignment -name VIRTUAL_PIN ON -to *pipe_sim_only*

set_instance_assignment -name IO_STANDARD "3.0-V LVTTL" -to pcie_rstn_pin_perst

ensure pcie_rstn_pin_perst is whatever this port is called in your top level.

the information contained within the S10 PCIe Example Design User Guide,

can you ensure that you have the following two assignments in your test project:

Regards

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Wincent,

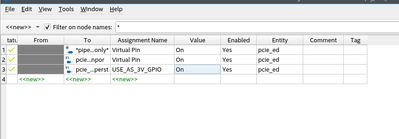

I just confirmed that both constraints are present in my QSF.

Additionally, the pcie_rstn_pin_perst pin is connected to the top level interface.

I have attached the QAR file here.

Regards,

Arley

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi,

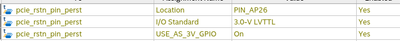

Thank for your response, I assume the same error still happen right ? the problem seen more clear to me.

In that case, There is a method on my mind that worth to try for us to narrow down more further

- Can you please try set_instance_assignment -name USE_AS_3V_GPIO ON -to <your pin name>

- this was specified in S10 IO UG: https://www.intel.com/content/www/us/en/docs/programmable/683518/21-2/guideline-i-o-standards-limitation-for-and.html

- Also same problem been reported in KDB before https://www.intel.com/content/www/us/en/support/programmable/articles/000091170.html

Let me know if this helpful. Looking forward to hear back from you.

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi,

I wish to follow up with you about this case.

May I know if the error still occurs again?

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi,

We do not receive any response from you to the previous answer that I provided.

This thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Otherwise, the community users will continue to help you on this thread. Thank you

If you feel your support experience was less than a 9 or 10,

please allow me to correct it before closing or please let me know the cause so that I may improve your future support experience.

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Wincent,

Sorry for my late response.

I have tried your suggestion

And I still didn't get a the perst pin placed by the tool.

Regards,

Arley

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Arley,

Is okay, I still remain this open for three days after my last message in case you reach back.

I see there is a three settings for the pin, if follow the KDB provided.

Can you please just remove other settings that you make before but remain the "set_instance_assignment -name USE_AS_3V_GPIO ON -to pcie_rstn_pin_perst" ONLY as per mention in the KDB ?

To avoid any miss match, I would suggest you to generate a brand new design for that.

Hoping to hear back from you.

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Wincent,

I have created a new project based on example design and set the USE_AS_3V_GPIO according to your suggestion and the problem continue.

Have you see the QAR file that I sent you?

Have you seen similar issues on that?

Regards,

Arley

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Arley,

Please allow me to have sometime to investigate on this issue.

Get back to you soon as possible.

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

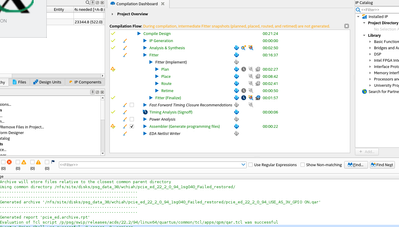

Hi Arley,

Apologize for late reply, I use the .qar file provided by you pcie_ed_22_2_0_94_1sg040_Failed.qar

Initially it fail, I got the exact error as you, but after implementing the solution stated in the KDB.

I was able to run 100 % full compilation without any error

Could you please try it again ?

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Attach with the success .qar file

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Arley,

Are you able to run the full compilation with the solution I provided?

Do you still have any questions on this?

Else I would like to have your permission to close this ticket from my side.

Hoping to hear back from you.

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi,

I wish to follow up with you about this case.

Do you have any further questions on this matter ?

Else I would like to have your permission to close this forum ticket

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Arley,

We do not receive any response from you to the previous answer that I provided.

Also, I strongly believe that my previous answer had solve your problem (Please correct me if I am wrong)

Hence, This thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Otherwise, the community users will continue to help you on this thread. Thank you

If you feel your support experience was less than a 9 or 10,

please allow me to correct it before closing or let me know the cause so that I may improve your future support experience.

Regards,

Wincent_Intel

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Wincent,

Sorry again for my late response. I have tested and it is solved.

Thank so much for your great support.

Regards,

Arley

- RSS-Feed abonnieren

- Thema als neu kennzeichnen

- Thema als gelesen kennzeichnen

- Diesen Thema für aktuellen Benutzer floaten

- Lesezeichen

- Abonnieren

- Drucker-Anzeigeseite