- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

we want to properly constrain our application logic of a design using the H-Tile Avalon Streaming PCIe Hard IP-Core.

The Application Logic is driven by coreclkout_hip then later we have some clock domain crossing logic to transfer data to a lower 50MHz Clock.

I tried to properly constrain the design, especially the asynchronous clock transfers according to this guideline https://www.intel.com/content/www/us/en/docs/programmable/683353/21-3/clock-domain-crossing-constraint-guidelines.html

However, I've failed to identify the clock associated with output pin coreclkout_hip in the report_clocks output of the timing analyzer, in order to e.g. specify the coreclkout_hip and 50Mhz clock as asynchronous using the set_clock_groups command.

Do I need to define the coreclkout_hip clock myself in my constraints file using the create_clock or create_generated clock myself or is the clock already defined by the constraints file of the IP-Core?

If the latter is the case, how do I identify the defined clock that corresponds to coreclkout_hip?

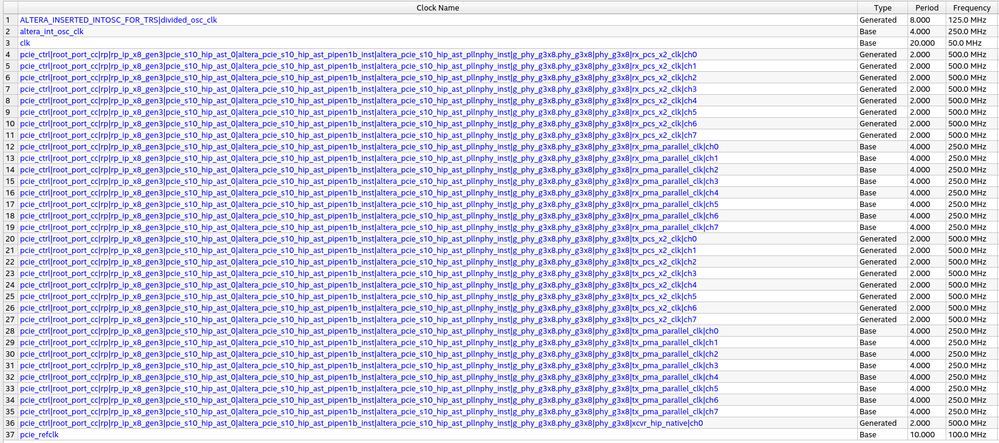

I've put the output of the report_clocks command below. Please let me know if you need any further information regarding our design.

Kind regards.

ALTERA_INSERTED_INTOSC_FOR_TRS|divided_osc_clk

altera_int_osc_clk

clk

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pcs_x2_clk|ch0

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pcs_x2_clk|ch1

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pcs_x2_clk|ch2

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pcs_x2_clk|ch3

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pcs_x2_clk|ch4

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pcs_x2_clk|ch5

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pcs_x2_clk|ch6

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pcs_x2_clk|ch7

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pma_parallel_clk|ch0

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pma_parallel_clk|ch1

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pma_parallel_clk|ch2

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pma_parallel_clk|ch3

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pma_parallel_clk|ch4

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pma_parallel_clk|ch5

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pma_parallel_clk|ch6

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|rx_pma_parallel_clk|ch7

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pcs_x2_clk|ch0

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pcs_x2_clk|ch1

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pcs_x2_clk|ch2

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pcs_x2_clk|ch3

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pcs_x2_clk|ch4

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pcs_x2_clk|ch5

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pcs_x2_clk|ch6

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pcs_x2_clk|ch7

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pma_parallel_clk|ch0

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pma_parallel_clk|ch1

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pma_parallel_clk|ch2

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pma_parallel_clk|ch3

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pma_parallel_clk|ch4

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pma_parallel_clk|ch5

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pma_parallel_clk|ch6

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|tx_pma_parallel_clk|ch7

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|xcvr_hip_native|ch0

pcie_refclk

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

For the coreclkout_hip you may refer to under 6.1.3. Clocks and Reset

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_s10_pcie_avmm.pdf

If you are using avmm HIP, coreclkout_hip can be used for the application logic.

coreclkout_hip clock should be used as the clock for PCIe "user" logic.

Hope this clarified.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to the timing analyzer the logic I clock with coreclkout_hip has the following clock as clock input:

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|xcvr_hip_native|ch0

However the clock is a 500MHz clock according to the Timing Analyzer, whereas the User Guide states that coreclkout_hip is a 250MHz clock, if the IP-Core is configured as Gen3 x8.

The following picture shows the timing analyzers clocks summary output (the clock in questions is at row number 36):

There is another post in the forums where it is discussed why the clock is shown as a 500MHz clock:

If I understand it correctly the conclusion of the discussion was, that coreclkout_hip is a 250MHz clock as stated in the User-Guide, and the clock shown by the timing analyzer is a clock internal of the PCIe HIP Core.

Is this correct?

My confusion as of how I constrain my logic driven by coreclkout_hip remains. Can I safely refer to

pcie_ctrl|root_port_cc|rp|rp_ip_x8_gen3|pcie_s10_hip_ast_0|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|xcvr_hip_native|ch0

in my timing constraints as if it were coreclkout_hip, despite the frequency difference?

If not how to I create a proper clock target for coreclkout_hip?

Please let me know if I can provide you with any further information.

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am the same Application Engineer who providing answer at the below forum (that you sent in this reply)

Yes, your understanding is correct for "coreclkout_hip is a 250MHz clock as stated in the User-Guide, and the clock shown by the timing analyzer is a clock internal of the PCIe HIP Core."

There is some confusing between the timing report comparing to the userguide, I will report to internal team again, hope they will fix this either in Quartus/user guide to avoid causing any confuse.

Regards,

Wincent_Intel

p/s: If any answer from the community or Intel Support is helpful, please feel free to give the best answer or rate 9/10 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Thanks for confirming the answer, glad that I am able to help you.

Hence, I will close my loop on this case and this thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Otherwise, the community users will continue to help you on this thread. Thank you

If your support experience falls below a 9 out of 10, I kindly request the opportunity to rectify it before concluding our interaction. If the issue cannot be resolved, please inform me of the cause so that I can learn from it and strive to enhance the quality of future service experiences.

Regards,

Wincent_Intel

p/s: If any answer from the community or Intel Support is helpful, please feel free to give the best answer or rate 9/10 survey.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page