- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

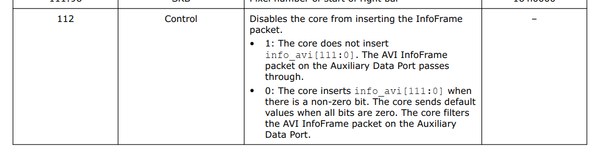

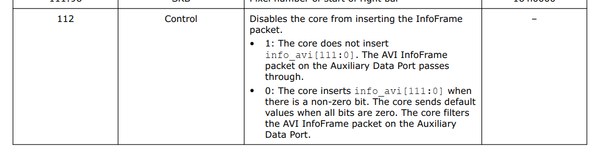

According to the HDMI Intel® FPGA IP User Guide (Table 24), the info_avi[112] is the control bit, which define whether the HDMI Core insert/filter packets on the Auxiliary Data Port.

But, in the HDMI Example Design, the info_avi[112] is connected to the ~user_pb_2 signal, which is defined as a virtual pin:

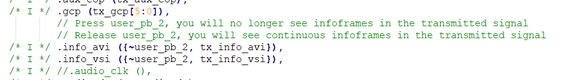

Here is from file c10_hdmi2_demo.v, line 512:

.info_avi ({~user_pb_2, tx_info_avi}),

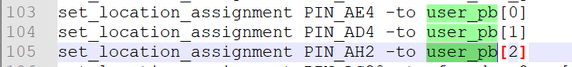

Here is from the c10_hdmi2_demo.qsf (user_pb_2 is assigned to user_pb[2] in another file):

set_instance_assignment -name VIRTUAL_PIN ON -to user_pb[2]

So, how should this work? Why is the info_avi[112] control bit assigned to a Virtual Pin?

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

>Will the infoframe packet be sent out when info_avi[112]=1and blocked/filtered out when info_avi[112]=0?

I believe the above statement is incorrect.

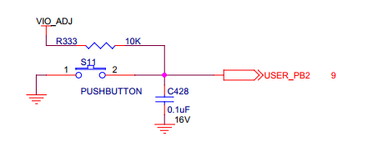

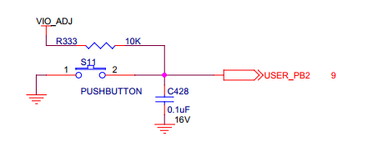

Based on the Cyclone 10GX schematic file:

and the HDMI IP User Guide:

when info_avi=1, it will not insert the Infoframe.

With that, the Infoframe packet will be sent out when info_avi[112]=0 (user_pb_2=1, released) and blocked/filtered out when info_avi[112]=1 (user_pb_2=0, pressed) .

Hope this answer your question.

Thank you.

Best Regards,

ZulsyafiqH_Intel

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Any response?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Thank you for reaching out.

Yes, you are correct, the info_avi[112] is the control bit.

After checking from my side, from file c10_hdmi2_demo.v, line 481:

.info_avi ({~user_pb_2, tx_info_avi}),

From file c10_hdmi2_demo.qsf, the info_avi[112] control bit assigned to pin AH2.

May I know your Quartus software version?

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using the Quartus v19.3, in the generated by me Example Design this pis is assigned to Virtual Pin.

Why this signal is assigned to the external pin? What purpose for?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

It is best to use latest version of Quartus.

>Why this signal is assigned to the external pin? What purpose for?

Based on HDMI example design, this pin is connected to the user pushbutton to control a feature where you can see or unsee the infoframes in the transmitted signal.

This example design uses this input to control this feature.

From c10_hdmi2_demo.v file, you can see below comment:

Hope this answer your question.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ZulsyafiqH_Intel,

In the last post you wrote: "From c10_hdmi2_demo.v file, you can see below comment:", but you did not add the mentioned comments....

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Will the infoframe packet be sent out when info_avi[112]=1 and blocked/filtered out when info_avi[112]=0 ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

>Will the infoframe packet be sent out when info_avi[112]=1and blocked/filtered out when info_avi[112]=0?

I believe the above statement is incorrect.

Based on the Cyclone 10GX schematic file:

and the HDMI IP User Guide:

when info_avi=1, it will not insert the Infoframe.

With that, the Infoframe packet will be sent out when info_avi[112]=0 (user_pb_2=1, released) and blocked/filtered out when info_avi[112]=1 (user_pb_2=0, pressed) .

Hope this answer your question.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

I wish to follow up with you about this case. Do you still have further inquiries on this issue?

I will remain this loop open for 2 days.

If we do not receive any response from you to the previous answer that I have provided.

This thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Otherwise, the community users will continue to help you on this thread.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

please don't close this thread.

I want to test your solution on the board, but I'll back to the office only in the middle of the next week.

So, please don't close this thread till end of next week.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

I wish to follow up with you about this case.

Did you manage to test the solution?

Hoping to hear back from you so that we can proceed for next step.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

I wish to follow up with you on this case. Do you still have further inquiries on this issue? I will remain this loop open for 2 days.

If we do not receive any response from you to the previous answer that I have provided.

This thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Otherwise, the community users will continue to help you on this thread.

Thank you

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm going to test the proposed configuration on the board till end of the week, so meanwhile please don't close the case, thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

I wish to follow up with you about this case.

Do you still have further inquiries on this issue?

Hoping to hear back from you so that we can proceed for next step.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

you can close this case, thank you for your support!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page