- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

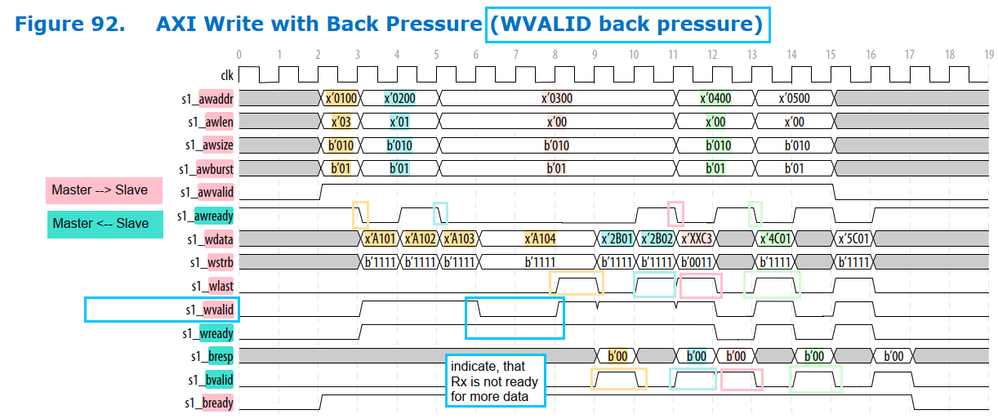

I am referring to the AXI Write timing diagrams (Figure 92 / 93) in the "Embedded Peripherals IP User Guide" on p. 331.

I believe there is a confusion between the **VALID and **READY signal usage and the wrong signals are used to indicate back pressure. Because the "pressure" is indicated by the Slave "back" to the Master interface and should therefore use signals of the direction Slave --> Master.

Figure 92. uses the s1_wvalid signal to indicate back pressure (by going low on the 6th clk). This signal's direction is Master --> Slave. Instead, it should be s1_wready that is Slave --> Master.

Figure 93. uses the s1_bready signal to indicate back pressure (by staying low at the 7th clk until the 10th clk). This signal's direction is Master --> Slave. Instead, it should be s1_bvalid that is Slave --> Master.

Is this really a mistake in the timing diagrams or did I understand the concept of "back pressure" wrong? Because the way it is displayed now, the Master indicates to the Slave that it is not ready to send instead of the Slave indicating to the Master that it is not ready to receive.

- Tags:

- AXI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Simon,

You are correct that in the AXI protocol, back pressure is indicated by the slave to the master using the ready signals, and not the valid signals. So, in both Figure 92 and Figure 93, the direction of the ready signals is seem to be incorrect. The s1_wready signal should be used to indicate back pressure in Figure 92, and the s1_bvalid signal should be used to indicate back pressure in Figure 93.

It seems like there might be an error in the timing diagrams which I will file a documentation enhancement. Thank you for bringing this to attention.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Simon,

You are correct that in the AXI protocol, back pressure is indicated by the slave to the master using the ready signals, and not the valid signals. So, in both Figure 92 and Figure 93, the direction of the ready signals is seem to be incorrect. The s1_wready signal should be used to indicate back pressure in Figure 92, and the s1_bvalid signal should be used to indicate back pressure in Figure 93.

It seems like there might be an error in the timing diagrams which I will file a documentation enhancement. Thank you for bringing this to attention.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 5/5 survey

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page