- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I try to generate a NIOSII system with the following configuration using Quatus v17.1:

- NIOSII gen2 processour (reset vector and exception vector addresses are located in the onchip memory)

- Onchip memory: (data width = 32 bits and ECC = enabled, So the data width becames = 39 bits )

- JATG UART

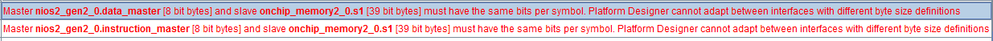

When I started the generation of the HDL files on the Platform Designer, I got the following errors :

Any advice please ?

Link Copied

2 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I will check with our internal team and let you know the feedback soon,

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

On chip memory ECC is not supporting Nios II connection.

Thanks

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page