- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

My problem is that the component altera_emif_c10 (DDR3) doesn't complete reads with burstcount[..] set to more than 1.

According to Avalon-MM interface protocol burst writes and reads are conducted using burstcount[..] and beginburst signals. But altera_emif_c10 component doesn't provide beginburst signal. And also I failed to find the parameter max burst lenght in altera_emif_c10. So it's hard to imagine what are the supported values of the burst lenght.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear MEmel1,

Please accept my apology for the delay in response due to recent workload.

Actually the parameter is hidden in the altera_emif_c10 GUI. You can go to your top right of the GUI (beside Generate Example Design tab) --> right click --> click show hidden parameter and you should be able to see the parameter of max burst length in the GUI.

Also, you may refer to this Cyclone 10 EMIF user guide for more info --> https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20116.pdf

Hope this helps. Feel free to let me know if you have any concern.

Again I sincerely apologize for the delay in response.

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, NAli1,

Thank you for your answer!

I managed to find maximum burst length parameter in hidden parameters. It's set to 4. So theoretically everything should have been working already..

But what about burstbegin signal? How burst write/read should be initiated without burstbegin signal?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MEmel1,

You are more than welcome. 😊

There is a burstbegin signal in the Avalon-MM slave port. This is covered in the user guide I provided just now in Table 32 (page 48) under Chapter 3 in the user guide.

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

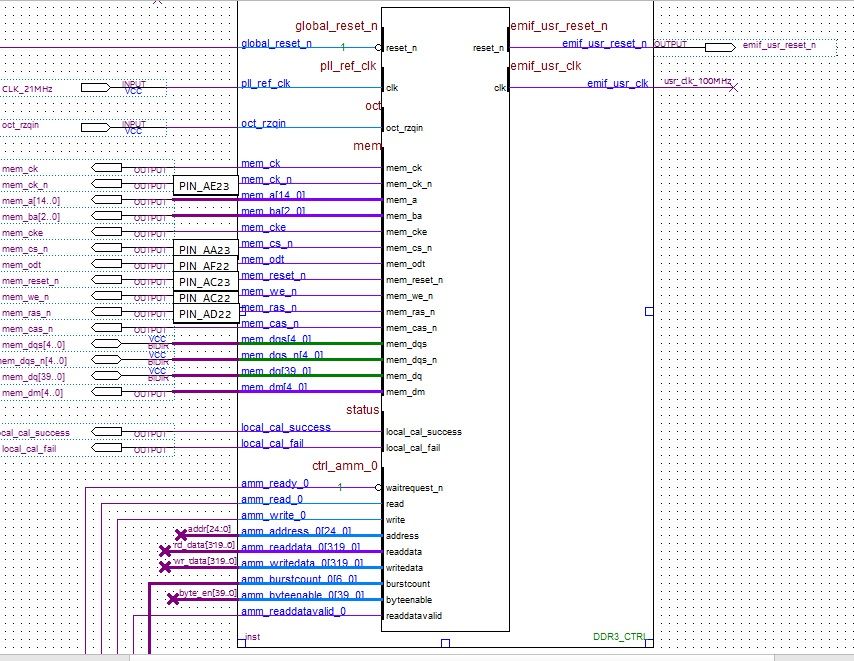

Yes, there should be burstbegin signal according to the documentation you provided. But it's not present in my component schematic. May be there's also an oprion to make it visible?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear MEmel1,

The burstbegin signal is redundant. When the amm_write start issue write request signal and it start to initiate the burst begin signal. And user can control the burst by setting the burst count.

You may want to try run simulation on the example design to get clearer picture on the timing diagrams and how the signal operate on the example design.

Hope this helps.

Thanks

Regards,

NAli1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page