- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

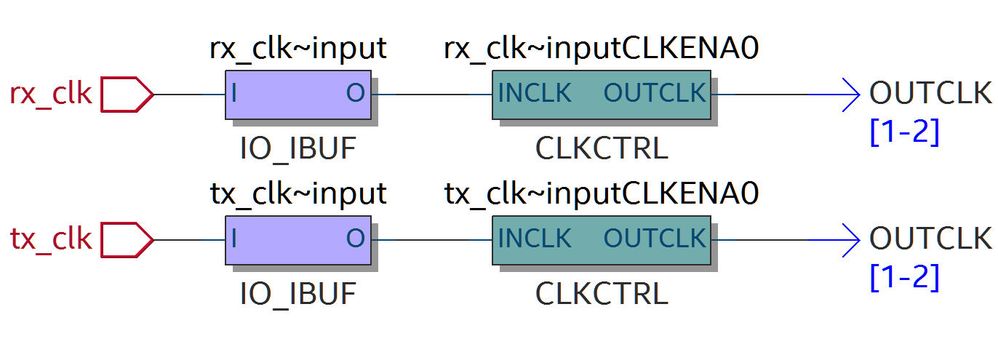

I'm using the Altera Tri-Mode EMAC for 10/100 Ethernet with MII interface to the Phy. This uses 25 MHz tx_clk and rx_clk generated by the Phy and going to the EMAC. These clocks do NOT use dedicated clock inputs. The EMAC puts them on clock nets using ALTCLKCTRL as follows:

I want to use a Phy with an RMII interface which has a single 50 MHz clock from the Phy. I have an RMII to MII bridge which generates tx_clk and rx_clk. I can of course use a PLL, but that requires a dedicated clock input and I'm short on pins.

So I'm looking for another way. On Xlinx, I can use a BUFR which allows dividing. So far on Altera, the only solution of come up with is to use an ALTCLKCTRL fed by a registers:

-----------------------------------------------------------------------------

-- Divide the RMII clock by two

-----------------------------------------------------------------------------

mii_clk_proc : process

begin

wait until rising_edge(rmii_clk); -- 50 MHz clock from Phy

clk_div2 <= not clk_div2; -- 25 MHz "clock"

end process;

-- Drive ALTCLKCTRL to put clk_div2 on globacl clock

rmii_clk_ctrl : component phy_clk_ctrl

port map (

inclk => clk_div2,

outclk => mii_clk -- drives both tx_clk and rx_clk

);But this seems like a really bad way to do this. Any suggestions?

Another problem is that whether I use a PLL or the above, the EMAC is still using two ALTCLKCTRL as above. These really should not be needed.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @sreekumar.regu.girijakumari ,

Yes, the clk_div2 register is adding alot of delay. About 8 ns. So I needed to add FIFO's to buffer between the MII clocks and RMII clock.

For the most part, Xilinx IP is incredibly cumbersome and poorly designed compared to Altera, but they have some nice features such as the BUFR. It occurred to me I might use the clk_div2 as an enable for the ALTCLKCTRL instead of the input. But in the end, it's probably best if I have enough PLL's and clock inputs to avoid the problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@sreekumar.regu.girijakumari , Using the enable is not a good solution. I'm forced to use a PLL for this purpose.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page