- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I m trying to establish a fiber link between two FPGA board (MAX10M08) via a SFP-6 comnet fiber module. I'm using soft LVDS FPGA IP core for serialization and deserialization of the data. My data rate is 1Mbps(1MHZ) and I'm trying to Manchester encode the data to higher frequency closer to 1GHZ to send over fiber link( since SFP transmits the signal at 1GHZ and requires minimum drive speed of 125Mbps ). I was wondering, if I simply XOR the serialized data with the higher frequency ( above 500MHZ) before transmitting, will it work? And how would be the corresponding receiving circuitry?

Any suggestions will be highly appreciated.

Thank you .

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Well if this is the case, i would recommend you use the LVDS IP on both transmitting and receiving side. You can write your RTL design as well but it would be better if you could leverage the IP.

THank YOu.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Thanks for the suggestion. I have been using LVDS IP on both transmitter and receiver side. But, the system works occasionally only. Sometime there is no reception at all and when there is, the data recovered is not aligned and not in order. I tried with sending a 10 bit counter data and what I receive on the receiver side is random data between 1 to 1023. I was wondering if there is any way to align and recover the data on receiver side and make sure the reception is not occasional.

Thank You

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Keshav,

On the receiver side, have you used DPA mode? You might need to enable those setting and do some setting in order to receive signal correctly. You may take a look at our user gude for that.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_altera_lvds.pdf

Thank You.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SooY,

Thank You very much for the reply. But unfortunately there is no DPA mode availabe for MAX10 M08.

The LVDS IP available for MAX10 devices is soft LVDS intel FPGA IP. https://www.intel.com/content/www/us/en/programmable/documentation/sam1394433606063.html#sam1394435177990 .

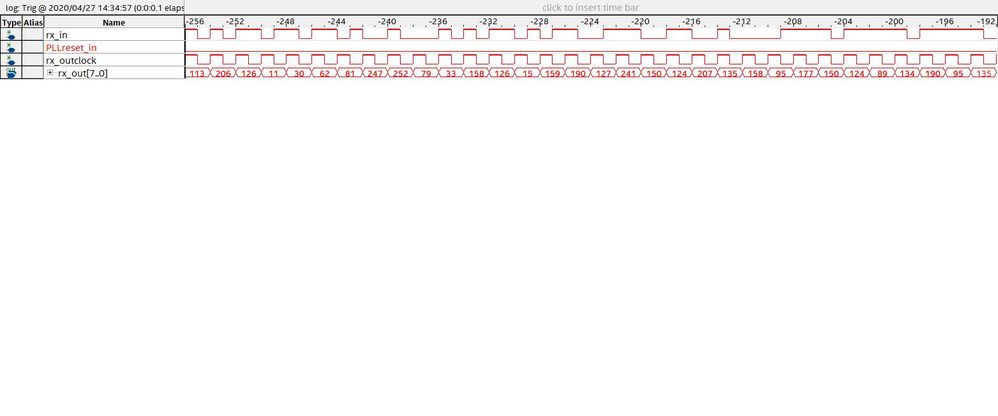

However, there is a data realignment circuit using RX_DATA_ALIGN pulse. Page 26,27. I have tried using it and tried using ISSP tool to pulse the RX_DATA_ALIGN signal (as advised on the link https://www.youtube.com/watch?v=02lgfcxSjQA&list=PLJCQGKgvE0JCr1W9vFL4phkvlPtWHlUVa&index=4&t=0s) but still no luck. The received signal as captured is

Any suggestion will be highly appreciated.

Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Keshav,

Can you try with a LVDS IP instead of the "simply XOR the serialized data with the higher frequency ( above 500MHZ) before transmitting". If it is working, that means to say the method you are using may not be appropriate.

Thank You,

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page