- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

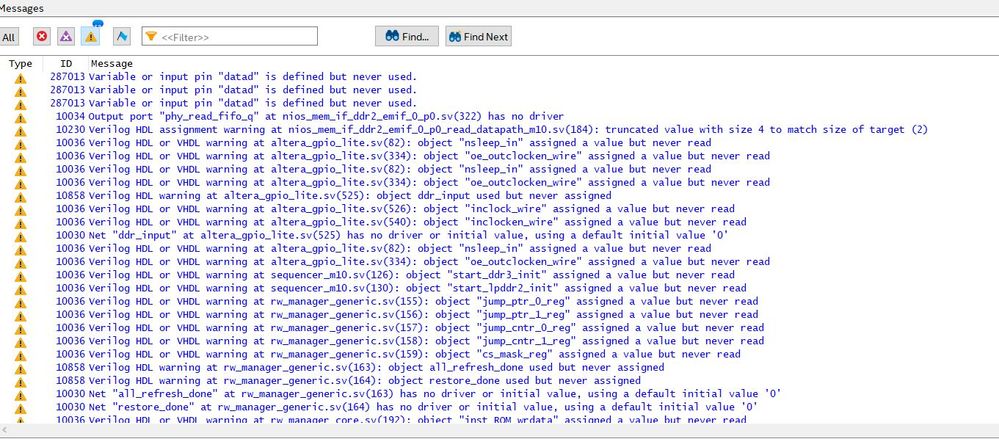

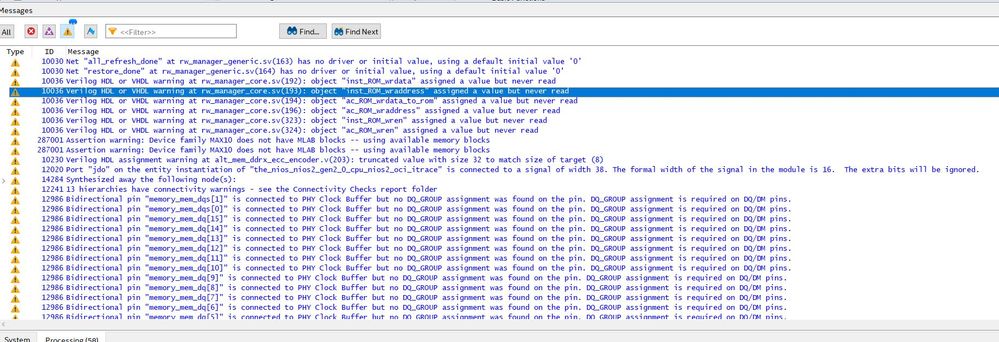

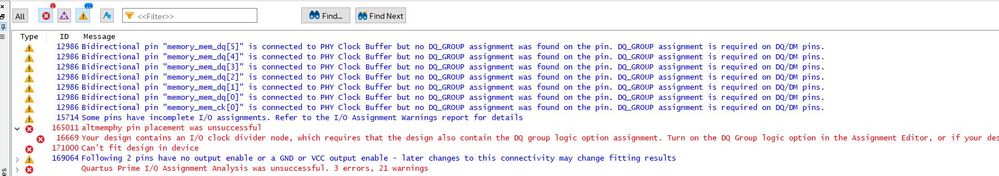

Use DDR2 controller with UniPHY

Integerate in platform design with NIOS.

Device used: Max10, 10M16DCU324I7G

Start analysis & Synthesis

How to handle below warmings?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

It seems to be a variable declaration issue and connectivity issue. I am suspecting this attributed to the warning.

Can the fitter compilation complete without error?-- If Fitter is Passing without error, then you can safely ignore the synthesis warnings.

You may find it useful to run the example design first, check the connection to help understanding and compare with your design.

I am attaching a word document which I centralized all the warnings listed with “CAUSE” and “ACTION” to help handle the warnings.

Hope this helps.

Thanks

Regards,

Aida

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

As there has been no update from you recently, I am assuming that the information I provided has helped you to resolve your issue. I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I still have problem , but I don't find where can set it in assignment editor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

You can refer to page 28 of this Quartus handbook --> https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/qts/qts_qii5v2.pdf

Please follow the steps provided to assign the Output Enable Group option.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page