Hello guys,

I am working on a design to use all 3000 DSP blocks on the stratix 10 FPGA. I thought the best solution would be to instantiate this intel fixed point DSP IP as a multiplier:

I am using a generate for loop to generate 3000 of these DSP's. The issue that I am having is that Quartus is optimizing away these blocks unless I directly connect each of the 3000 DSP's with a top level output.

I do not have enough IO on the board to accommodate 3000 outputs, so I just don't constrain the output signals to a pin. Quartus gives an error and will not synthesize the design since I am trying to synthesize more IO than I have on the board.

So I tried to use combinational logic to do something like:

output = DSP_out[0] || DSP_out[1] || DSP_out[2]

this actually does work, but it only synthesizes 3 DSP blocks....so I would need a long combination statement to include all 3000 DSP_out. I tried it also in a for loop and it does not work.

Here is my full code as it stands. I just need a way for all 3000 of the DSP blocks to synthesize. I hope my question makes sense.

SOLVED!!!!

I was assigning the output registers of each DSP block incorrectly.

What I had:

assign result1_a_r[i] = result1_a[i];

assign result1_b_r[i] = result1_b[i];

What it should be:

链接已复制

Hello,

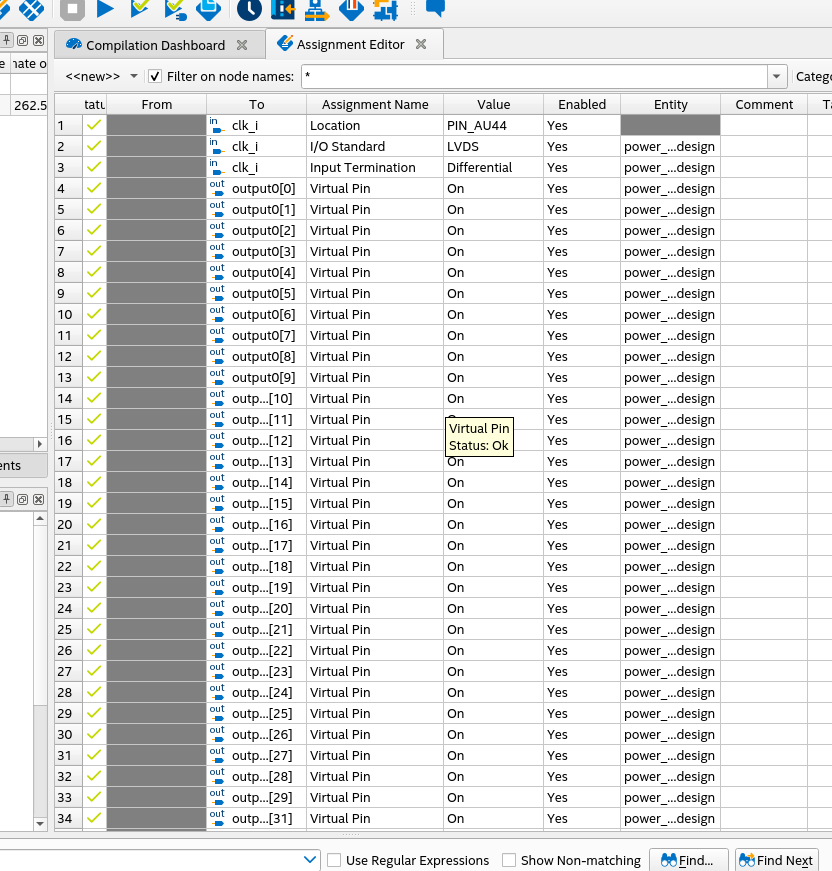

You could leave the DSP's at top level and use virtual pin assignment to fix the I/O problem.

https://www.intel.com/content/www/us/en/docs/programmable/683641/21-3/virtual-pins.html

Regards,

Nurina

Hello Nurina,

The output issue is solved by this trick, but i got bottlenecked at 468 DSP blocks.

I also tried chaining a lot of DSP blocks together (output from block1 as input of block2). This also works until I reach 468 DSP blocks. Then the place and route process fails with the message:

Error(184036): Cannot place the following 57 DSP cells -- a legal placement which satisfies all the DSP requirements could not be found

Info(184037): Node "GEN_DSP_2[0].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(184037): Node "GEN_DSP_2[132].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(184037): Node "GEN_DSP_2[133].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(184037): Node "GEN_DSP_2[134].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(184037): Node "GEN_DSP_2[135].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(184037): Node "GEN_DSP_2[136].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(184037): Node "GEN_DSP_2[137].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(184037): Node "GEN_DSP_2[138].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(184037): Node "GEN_DSP_2[139].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(184037): Node "GEN_DSP_2[140].U_DSP|s10_native_fixed_point_dsp_0|fourteennm_mac_component"

Info(18798): And 47 more similar nodes (full list omitted for brevity)

Here is the important parts of the updated code:

generate

Hello Nurina,

Attached is the .qar file.

I have commented out the last 2 DSP blocks in the chain to give a total DSP load of 450 blocks. This design builds fine(although it fails timing).

I recommend that you start with this build, and then comment out lines 499-502 and uncomment the block from lines 504-554. This will bring the total DSP count to 510 and the build will fail.

I cannot figure a way around this 468 bottleneck. I even tried instantiating another IP, the floating point DSP IP to split the load. No matter how I combined the fixed point and floating point IP's there was nothing I could do to achieve more than 468 DSP blocks.

Thanks

Jacob

SOLVED!!!!

I was assigning the output registers of each DSP block incorrectly.

What I had:

assign result1_a_r[i] = result1_a[i];

assign result1_b_r[i] = result1_b[i];

What it should be:

Hi Jacob,

I’m glad that your problem has been solved, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 4/5 survey

Regards,

Nurina