- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am trying to stream in data from an external source (through QSFP+) to the DDR4 memory and then do a DMA transfer the data to a Computer through PCIe.

For that I would like to use a FIFO to push data (that comes from QSFP+) into the DDR4 elements.

My plan is to integrate the Avalon FIFO Memory Intel FPGA IP with the PCIe DMA transfer example design mention in the Chapter-7 of the attached manual (DE5a-Net Arria 10 FPGA).

When try to add the FIFO IP to the example design in the System Builder, (here two "m0" master ports from Avalon MM Pipeline bridge Intel FPGA IP's (corresponding to two DDR4 memory) has to connect to the "out" slave port of the FIFO) I get a memory overlap error (Screenshot CaptureL1.png) when I did base address assignment to the "out" port. (Screenshot attached CaptureL2.png).

Any suggestion or comment regarding the way I try to do the integration of FIFO IP with the example design is most welcome. Also it would be great if someone could help me out of the slave address overlapping issue (generally how to allocate memory for a slave, when connecting to a master that already have a slave with an allocated memory) mentioned in the above paragraph. Feel free to ask any question if you need any further clarification of the problem.

PS: I am working in DE5a-Net-DDR4 Arria 10 GX (10 AX115N2F45E1SG) and use Quartus Prime Pro version 18.1

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

Thank you for submitting your question in Intel Community.

I'm Adzim from Penang Global Application Engineer will assist you in this thread.

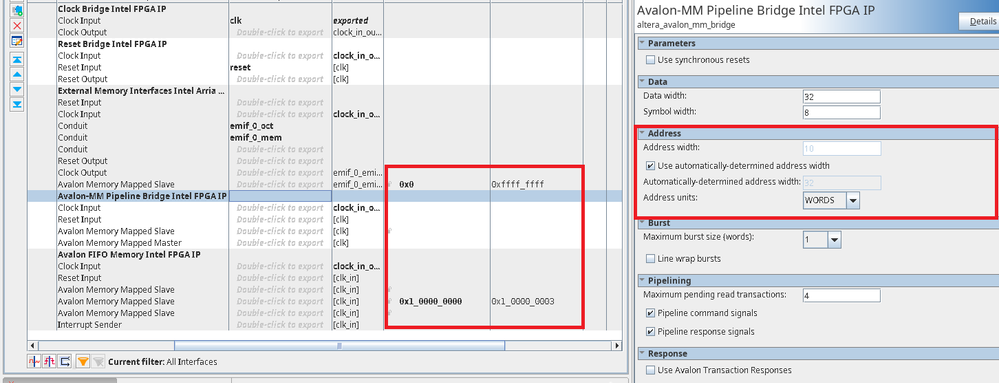

I've replicated the issues that you're facing and I think some settings in the Avalon Pipeline Bridge IP need to change.

- There is an option that you can use under the Address section -> Use automatically-determined address width. It's ease the user to determined the address width.

- I'm also advice you to use Address unit of WORDS. This can help the IP to improve the timing.

For the address overlapping issue, you can set the Base address of the Avalon FIFO Memory IP to 0x1_0000_0000 or higher to avoid the overlapping.

I hope that can resolve the problem.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

I would like to know if there is any update in this thread?

Please let me know if you have any further question.

Thank you.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Thank you for addressing my problem. Unfortunately that did not help me much.

I have some questions too. I already have the Address section -> Use automatically-determined address width enabled for Avalon Pipeline Bridge IP. Changing Address unit of WORDS gives some error "Port mismatch could not be auto resolved. Double click for manual resolution". We merged the interface and that resolved the errors.

Also, you suggested me to set the Base address of the Avalon FIFO Memory IP to 0x1_0000_0000 or higher to avoid the address overlapping. But I really would like to know you suggested me to do System->Assign Base Address (which I did and still problem persists. Screenshot attached 3.PNG ) or putting it manually. We put it manually and it says it's outside the master's address range.

Also, I noticed that the design you re-created (from the screenshot posted above) does not have some IP components like Avalon-MM Clock Crossing Bridge Intel FPGA IP (which is an IP in the QSYS file Demonstartions/PCIe_DDR4/ep_g3x8_avmm256_integrated.qsys while opening in System Builder).

I would like to explain the problem in bit more detail. I was trying to integrate a Avalon FIFO IP with the PCIe DMA Transfer Example design for Windows (Provided in DE5a-Net CD/Demonstrations/PCIe_DDR4/) mentioned in the Chapter-7 of the attached manual (DE5a-Net Arria 10 FPGA) attached as DE5a-Net_User_Manual.pdf. My objective is to stream data from QSFP+ to DDR4 memory, and then do a DMA transfer to a Computer through PCIe. I would also like to know if you could mention anything I have to be cautious in integrating an IP with a System Builder design.

I am explaining the step by step procedure I did

1. Opened th .qsys file of thePCIe DMA transfer example design (provided in the CD Demonstartions/PCIe_DDR4/ep_g3x8_avmm256_integrated.qsys) in System Builder.

2. Added Avalon FIFO IP with the example design. clk_in and reset_in are connected to global clock (Screenshot 1.PNG) --Can see message to connect fifo_15_in and fifo_15_out or export them.

3. Exported fifo_15_in port to connect tho QSFP+ later. You can see a warning message regarding the clock in screenshot 2.PNG (Could you mention how to get rid of this warning?)

4. Connected fifo_15_out with Avalon MM Pipeline bridge Intel FPGA IP's (corresponding to two DDR4 memory) . You can see the error messages regarding the memory overlap in screenshot 3.PNG -

5. Did System->Assign Base Address in System Builder and that did not resolve the issue. Then we tried putting it manually (the value you suggested `0x1_0000_0000`) and it says it's outside the master's address range.

6. Gets an additional error while changing Address unit from SYMBOLS to WORDS: "Port mismatch could not be auto resolved. Double click for manual resolution". Screenshot 4.PNG (We merged the interface and that resolved the errors)

Please let me know if you need any clarification. Any suggestion regarding my procedure to integrate IP with example design is also welcome.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @travisa ,

Thank you for your update and step by step procedure that have been provided.

I can reproduce the issues and I have debugged it from my end.

I believe that you should be able to get rid of the errors and warnings by following the recommendation that have been provided in Platform Designer.

You should run Sync System Infos to update the System Information for all IP components to check if there is any mismatch or to update the change.

I am attached the qsys file that contains the IP components.

The design should be clear from error messages.

Please let me know if you have any further question.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you very much for recreating my problem and sending me the file. I tried compiling it and succeeded. I would like to ask some questions regarding this. So I am explaining the steps I followed to run the .qsys file and attaching relevant screenshots.

1. I worked in my DE5a-Net "CD/Demonstrations/PCIe_DDR4/" folder and opened PCIe_DDR4.qpf Quartus Project file opened the ep_g3x8_avmm256_integrated.qsys in the System Builder.

2. Changed Address unit from SYMBOLS to WORDS for Avalon MM Pipeline Bridge IP and Avalon MM Clock-crossing Bridge IP. This throws an error as shown in CaptureA1.PNG. Resolved the port mismatch manually to resolve the errors.

I have a question regarding this step. What is the real cause of the error "Port mismatch could not be auto resolved. Double click for manual resolution" and what is the recommended solution for this. I it just merge option by double clicking the error?

Also, is there any reason other than improving the IP timing for changing Address unit from SYMBOLS to WORDS

3. I have added the Avalon MM FIFO IP and Clock Bridge IP to the design.

(I really would like to know is there any specific reason you used clock bridge IP to clock FIFO IP, instead of the clock from Clock IP or Clock from Avalon-MM DMA Hard IP?)

4. Connecting the out slave of FIFO IP with the masters from m0 from Avalon MM Pipeline Bridge IP. This gives the memory overlap issue. Would you please remind me why we should change the address specifically to 0x1_0000_0000 or higher?

By changing address to what you suggested removes error messages. Then ran the Generate HDL (as seen in CaptureA9.PNG (do we want to worry about the warning messages as seen in screenshot?) and then successfully compiled the project.

I am planning to make a custom IP that create random bits that should stream through FIFO to DMA and which in turn DMA transferred to a PC through PCIe. I there any thing we should be cautious in creating a custom IP that creates bits and feeds to FIFO?. Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi travisa,

"Also, is there any reason other than improving the IP timing for changing Address unit from SYMBOLS to WORDS "

No other reason than improving timing. If it's not working on your design, then you can still set Address unit with SYMBOLS. If there is some timing violation, later you can get some advice from Timing expert.

" (I really would like to know is there any specific reason you used clock bridge IP to clock FIFO IP, instead of the clock from Clock IP or Clock from Avalon-MM DMA Hard IP?)"

Because the input of the FIFO IP has been exported, the QSYS has recommended that the clock of FIFO IP need to be exported as well. But it's cannot be exported directly.

One of the recommendation here is to export the clock through a clock bridge or a clock source.

You can still connect it with a clock source.

"Would you please remind me why we should change the address specifically to 0x1_0000_0000 or higher?"

The master has connected with the emif and fifo. The address 0 - ffff_ffff has been used for emif. Then the fifo cannot overlap this address which is means it's should be higher than ffff_ffff.

"By changing address to what you suggested removes error messages. Then ran the Generate HDL (as seen in CaptureA9.PNG (do we want to worry about the warning messages as seen in screenshot?) and then successfully compiled the project."

It's good if you can take a look on it because the Quartus cannot perform the auto IP upgrade due to different Quartus edition and instead perform manual upgrade in the QSYS.

Then the Quartus will create another path to store the IP components that have been regenerated.

I have checked the missing parameter and it's actually exist in the code.

If you want to remove the warning messages, you can create another project and mimic the IPs that have been used.

"I there any thing we should be cautious in creating a custom IP that creates bits and feeds to FIFO?"

I'm not an expert on this area but I'm thinking that you should take care the data that will be connected to FIFO.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

Thank you very much for explaining things very well. I have a couple of quick questions too.

What is the real cause of the error "Port mismatch could not be auto resolved. Double click for manual resolution"? I it just merge option by double clicking the error? (Attached screenshot 7.PNG gets after double clicking the port mismatch message ). What is the recommended solution for this and what are the things we must consider in selecting between accept default or accept merge options in the screenshot.

Also, in the last e-mail, you mentioned "you should take care the data that will be connected to FIFO". Could you please elaborate it little bit? What are the specs. of data that I should take care?

Thanks again!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi travisa,

The error may appear when changing some of the Avalon parameter in the IP.

The QSYS will check the IP and the interconnect system to connect the port.

But the change may reflect to the IP only and the interconnect still has the previous value.

Then the QSYS will ask the user for checking on that if the new value should be used.

You can follow the recommendation that has been provided from QSYS to resolve the problem.

For FIFO IP consent, you can direct to FIFO IP user guide for the details.

There should be some specs and supported features that have been described in the user guide.

LINK: https://www.intel.com/content/www/us/en/docs/programmable/683522/18-0/fifo-user-guide.html

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous reply that we have provided, I now transition this thread to community support. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page