- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using Intel FPGA 16550 Compatible UART 16550 core to replace an old IP core, FIFOed UART, which is not available in Quartus 19.1 Standard Edition, Cyclone 10.

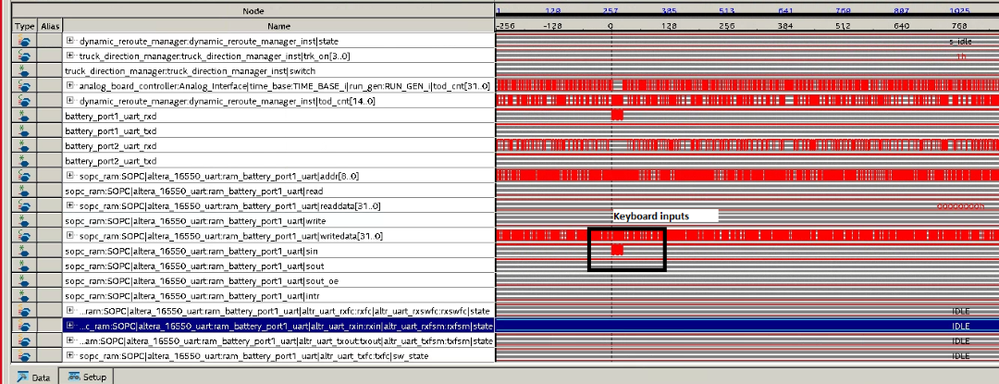

But the IP core is not working. My colleague writes the NIOS codes to write/read the registers fine, but no signals on the tx/rx line to external. I monitored signals using SignalTap and found out that all the state machines are not running. The attached image shows that all the states stayed idle even when there were inputs coming in. The total duration captured is 2 seconds.

I've purchased the license. Without license, Quartus generates a sof appended with "_time_limited". With license, it generates a normal named sof file.

Any help would be appreciated. Thanks.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

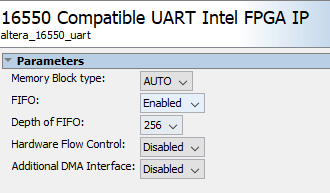

The IP core configuration is here:

Clock rate is 20.48 MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @JamesZhu

Sorry for the late reply. May I know do you able to solve your issue?

Do you still need help in regards to this case?

Best Regards,

Richard Tan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page