- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

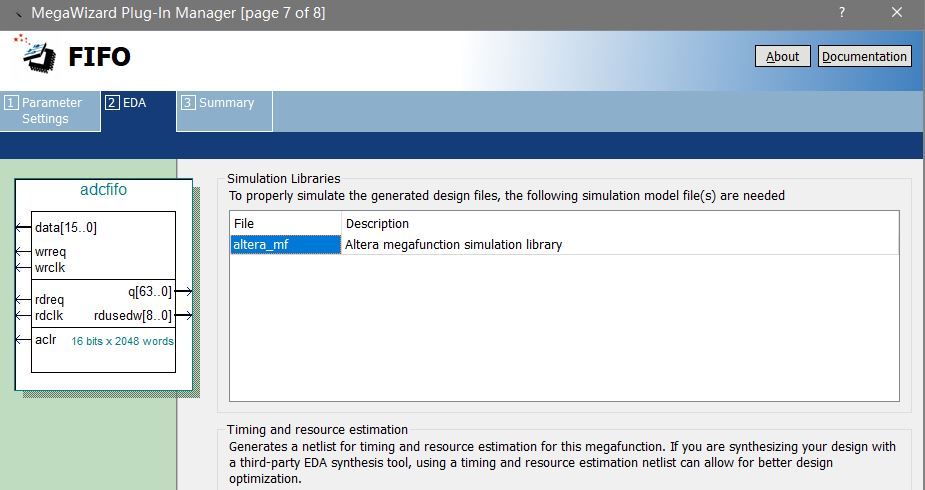

I defined a IP based on original Intel FIFO IP, and used in platform designer.

sink_clk, //50MHz

source_clk, //75MHz

reset_n,

sink_avalonst_data,

sink_avalonst_valid,

sink_avalonst_ready,

source_avalonst_data,

source_avalonst_valid,

source_avalonst_ready,

fifo_ready

);

input sink_clk;

input source_clk;

input reset_n;

input [15:0] sink_avalonst_data;

input sink_avalonst_valid;

output sink_avalonst_ready;

output [63:0] source_avalonst_data;

output source_avalonst_valid;

input source_avalonst_ready;

output fifo_ready;

/********************************************************************************************************************************\

part 0: Internal parameter

\********************************************************************************************************************************/

wire [8:0] rdusedw;

/********************************************************************************************************************************\

part 1: FIFO

\********************************************************************************************************************************/

adcfifo fifo(

.data (sink_avalonst_data),

.wrclk (sink_clk),

.wrreq (sink_avalonst_valid),

.q (source_avalonst_data),

.rdclk (source_clk),

.rdreq (source_avalonst_ready),

.rdusedw (rdusedw),

.aclr (~reset_n)

);

assign source_avalonst_valid = rdusedw[8] & reset_n;

assign sink_avalonst_ready = (rdusedw < 9'd511);

assign fifo_ready = rdusedw[8] & reset_n;

It can not be successfully simulated in modelsim-intel. Based on IP, it requires altera_mf.

This is already in modelsim searched libraries. So I don't know why it still fails.

The error message is as below. adcfifo is qip I generated based on Intel FIFO IP.

adc_fifo.v(41): Instantiation of 'adcfifo' failed. The design unit was not found.

# Searched libraries:

# C:/intelFPGA/18.0/modelsim_ae/altera/verilog/altera

# C:/intelFPGA/18.0/modelsim_ae/altera/verilog/220model

# C:/intelFPGA/18.0/modelsim_ae/altera/verilog/sgate

# C:/intelFPGA/18.0/modelsim_ae/altera/verilog/altera_mf

# C:/intelFPGA/18.0/modelsim_ae/altera/verilog/altera_lnsim

# C:/intelFPGA/18.0/modelsim_ae/altera/verilog/fiftyfivenm

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

adc_fifo.v(41): Instantiation of 'adcfifo' failed. The design unit was not found.

I guessing line 41 start from here:

adcfifo fifo(

.data (sink_avalonst_data),

.wrclk (sink_clk),

.wrreq (sink_avalonst_valid),

.q (source_avalonst_data),

.rdclk (source_clk),

.rdreq (source_avalonst_ready),

.rdusedw (rdusedw),

.aclr (~reset_n)

);

Modelsim can't find the so-called adcfifo.v file and I guess the adcfifo.v is in the adcfifo.qip that you generated based on Intel FIFO IP. Add the qip in your project, compile and simulate again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, the adcfifo.v is in the qip files. Actually I already include qip in below two methods, but it still doesn't work.

1) add qip through assignment - > setting - > files

2) add qip in platform designer -> component editor -> files -> both synthese file and simulation files.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Which Quartus version are you using? Standard or pro?

Could you share your project so I can investigate further? A simplified design that can duplicate the issue will do.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quartus prime 18.0, standard version.

I just solved the issue by adding adcfifo.v in the component editor simulation files.

1) Add adcfifo.v --> it works.

2) Add adcfifo.qip --> it doesn't work.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page