- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

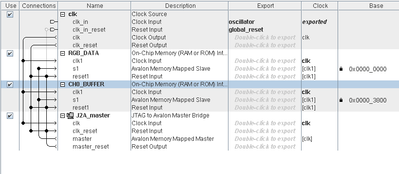

We have Qsys design with JTAG to Avalon Master Bridge and On-chip memory targeted to MAX10 Dev Board.

Could not access memory through system console. seeing following error

SEVERE: master_read_memory: This transaction did not complete in 60 seconds. System Console is giving up.

Could access JTAG loopback, sample clock, sample reset from system console.

Any help will be really useful.

Thank you

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

(Platform Designer, not Qsys)

Did you set up the master service path in System Console and claim the service? What are the commands you've issued in System Console?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell

Thanks for the Response

I have set the master service and claim the path. I have used below commands in system console also pasted response.

Using Max10M50DA dev kit.

Pin loc clock is M8 (25MHz)

Pin loc reset_n is D9

% set jd_path [lindex [get_service_paths jtag_debug] 0]

/devices/10M50DA(.|ES)|10M50DC@1#USB-1/(link)/JTAG/(110:132 v1 #0)/phy_0

% jtag_debug_sample_clock $jd_path

1

% jtag_debug_sample_clock $jd_path

0

% jtag_debug_sense_clock $jd_path

1

% jtag_debug_sample_reset $jd_path

1

% jtag_debug_loop $jd_path [list 1 2 3 4 5 6 7 8 9 10]

0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x0a

% jtag_debug_reset_system $jd_path

% jtag_debug_sample_reset $jd_path

1

% set ocram 0x0

0x0

% set m_path [lindex [get_service_paths master] 0 ]

/devices/10M50DA(.|ES)|10M50DC@1#USB-1/(link)/JTAG/(110:132 v1 #0)/phy_0/master

% set c_path [claim_service master $m_path ""]

/channels/local/(lib)/master_1

% master_read_32 $c_path $ocram 1

error: master_read_32: This transaction did not complete in 60 seconds. System Console is giving up.

while executing

"master_read_32 $c_path $ocram 1"

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your $ocram Tcl variable becomes a string variable because of the "x", so that's probably why the command is failing. Just put the address itself in the master_read_32 command to test. If you're going to need a variable for this address in a script, you'll probably need to do some Tcl "finagling". I like the Tcl reference here: http://tmml.sourceforge.net/doc/tcl/index.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for sharing Tcl reference.

I have tried with below command as well but still errored out

master_read_memory $c_path 0 32

Do we need valid quartus license for program and debug?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You don't need a license for this. Could the design be stuck in reset? You got 1 back from the jtag_debug_sample_reset command.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes. I did get 1 back from jtag_debug_sample_reset command

I have pasted commands and responses below.

% jtag_debug_sample_clock $jd_path

0

% jtag_debug_sample_clock $jd_path

1

% jtag_debug_sample_reset $jd_path

1

% jtag_debug_reset_system $jd_path

% jtag_debug_sample_reset $jd_path

1

% set m_path [lindex [get_service_paths master] 0]

/devices/10M50DA(.|ES)|10M50DC@1#USB-1/(link)/JTAG/(110:132 v1 #0)/phy_0/master

% set claim_path [claim_service master $m_path ""]

/channels/local/(lib)/master_1

% master_read_32 $claim_path 0 1

error: master_read_32: This transaction did not complete in 60 seconds. System Console is giving up.

while executing

"master_read_32 $claim_path 0 1"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Changed the clk pin from 25MHz board clock to 50MHz clock.

Now able to read and write to memory

% master_read_32 $claim_path 0 1

0x00000000

% master_write_8 $claim_path 0x0 0xe

% master_read_32 $claim_path 0 1

0x0000000e

Thank you very much for your support

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page