- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey,

I'm trying to integrate the Remote Upgrade IP in Cyclone V without an Avalon bus and I have two questions:

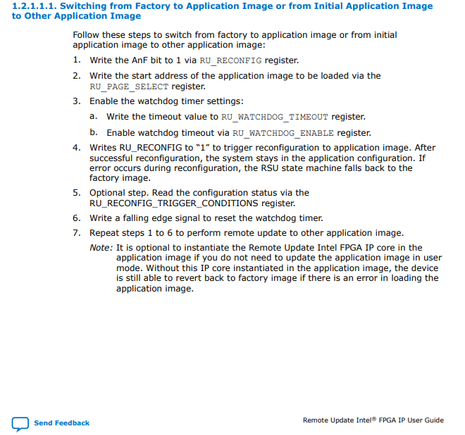

1) Do I need to integrate the Remote Upgrade IP in the factory design with a state machine that operates it according to page 7 in the user guide ?

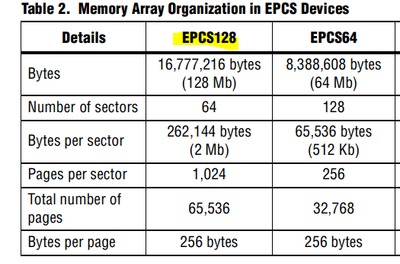

2) I'm working with a EPCS128 device so what are the address range of page 0 (the factory image) and page 1 (image 2-application image) ?

Thank you very much!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please find my response below:

1) Do I need to integrate the Remote Upgrade IP in the factory design with a state machine that operates it according to page 7 in the user guide ?

Yes, you need to.

2) I'm working with a EPCS128 device so what are the address range of page 0 (the factory image) and page 1 (image 2-application image) ?

I am assuming you are using Active Serial Configuration Scheme. When you are generating the bitstream for the flash (.jic), you may need to add 2 sof file (factory image and application image), from there, you can select the start address for page 0 and page 1.

Regards,

Bruce

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, I did it successfully.

Now, I want to add the option "Enable reconfig POF checking" so do I need check the "pof_error" signal in my state machine, before I send the reconfig command from my state machine to the Remote Update IP? I mean before the step 4 in the following order:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Lucky you are using a configuration device that supports Active Serial (AS) mode.

Our configuration device only supports FPP or PS scheme and we are using MAX V CPLD with PFL.

No luck from our side to use the Remote Update IP within our Cyclone V FPGA for this yet

Regards,

Kevin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes you can do so by reading the "pof_error" indicator before you trigger reconfiguration on steps 4.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I did it =).

Another question, if I give a wrong address to the Remote Update IP, how many addresses the ASMI Parallel IP will search before the "pof_error" indicator will turn on?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Another question, if I give a wrong address to the Remote Update IP, how many addresses the ASMI Parallel IP will search before the "pof_error" indicator will turn on?

The remote update IP will search for address that user entered only. If it is not existed, then "pof_error" indicator will turn on.

Regards,

Bruce

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page