- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

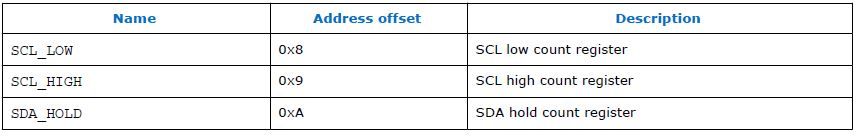

How can I determine SCL_LOW, SCL_HIGH, SDA_HOLD register value of Intel FPGA Avalon I2C Master Core?

I am planning to initialize the Core from my own designed sequencer.

Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

See attached.

You can refer to this document for more details. Let me know if you need further help.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_embedded_ip.pdf#page=173

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, I mentioned register value not the register location.

I am expecting all these timing is the timing while master driving SCL and SDA by itself.

I easily determine SCL_LOW and SCL_HIGH to define SCL waveform.

But I don't get what SDA_HOLD is.

I expect it is the time to sustain SDA from SCL low or high.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Let's say with a 100MHz input clock and the I2C Master is operating in normal mode of 100KHz.

For SCL_HIGH and SCL_LOW, the register value is (10us/10ns) divide by 2 assuming high and low is same (duty cycle 50:50). For SDA_HOLD, it is (your desired hold period/10ns).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a simple question for SDA_HOLD.

- is this timing spec when SDA as output or as input?

- is this timing spec for start/stop condition or data transfer?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page