- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I am trying to simulate the TSE testbench IP generated with Quartus Prime Standard 18.0. My simulator is Cadence Xcelium. Xcelium cannot decrypt the TSE testbench submodules.

I have not encountered this before with any of the other Quartus generated IP, but those may not have been encrypted (DDR2 controller for example).

Further investigation shows that all submodules for the TSE example testbench are broken out into ./Aldec or ./Mentor directories. This would explain why they cannot be decrypted by Cadence.

So is Cadence supported for the TSE testbench simulation? If so how do I generate the necessary files or how do I decrypt the files for Mentor or Aldec simulators.

Thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

- May I know which FPGA product that you are using here ?

- Can you share with me your TSE IP QSYS design file so that I know what setting that you are using in order to duplicate this sim issue ?

- May I know which Cadence Xcelium version that you use ? Based on TSE user guide, by right there should be another ./cadence or ./xcelium sim folder that you can use

- Also, have you try with latest Quartus version like Quartus Standard v19.1 to see if it helps to resolve issue ?

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi thanks for getting back to me-

- We are using a Cyclone V, 5CEFA9F31I7

- There was not a Qsys file. I did not use platform designer. I used the IP megawizard to generate the IP. So I generated it again using the platform designer. The results are the same. This system will not allow me to upload a Qsys file, so I had to add a .txt extension to it, hopefully it will remain useable when you remove that extension.

- We are using Xcelium 19.09. Yes I agree, I expected a ./Cadence and a ./Xcelium within the /Submodules directory. There is a ./cadence under the following path tse_testbench/testbench_verilog/tse_sim/cadence, however it only contains the cds.lib files and not the actual component submodules which I would expect to find under tse_testbench/testbench_verilog/tse_sim/submodules.

- Yes, I did install v19.1 and had the same results.

Thank you for your help.

Travis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Travis,

Thanks for sharing all the info.

Let me try to duplicate the sim run issue from my side.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Travis,

I think I figure out what's the issue now.

I cross check Quartus release note doc and found out Xcelium sim tool is only supported in Quartus Pro edition and not supported in Quartus Standard edition.

Attached is the screenshot of Quartus release note doc vs TSE sim model generated in example design.

- I used Quartus v19.1 standard edition to generate Cyclone V TSE example design

- Then I used Quartus v19.1 pro edition to generate Arria 10 TSE example design

Yet, Cyclone V is not supported in Quartus Pro edition as it's older generation FPGA.

So, I am afraid I need to ask you to switch to other simulation tool since you are using Cyclone V FPGA. if you are able to upgrade to newer generation FPGA like Arria 10 or Stratix 10, then it's fine to use Xcelium.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for taking the time to look into this. Unfortunately switching FPGAs is not an option nor is switching simulation tools. Both are VERY expensive.

However, There is still one avenue to look into. According to the tables you posted Cadence Incisive should still be supported. Xcelium is backward compatible with Incisive. So if those files were present I could use them. But they are not generated, so something is still not right. Can you try to find out why the Cadence Incisive submodules are not generated?

Thanks again.

Travis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Travis,

Sorry, I am not familiar with Cadence simulator tool. I checked Intel internal license. What we used is called Cadence NCSIM and when I launched the GUI, it showed as NClaunch.

- The sim model files is available in \eth_tse_0_testbench\testbench_verilog\eth_tse_0_testbench_sim\cadence\

Like wise, there is another "free" simulator that I can think of which comes together when you purchased Quartus license which is the "Modelsim Intel FPGA starter edition"

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Dlim, This is not a Cadence Problem it is a Quartus problem so you don't need to know anything about Cadence; I'll start over.

I am using Quartus Prime Standard, because I am using Cyclone V, which is not supported in Quartus Prime Pro.

The Triple Speed Ethernet submodules are encrypted. I'm not talking about the testbench model files, referenced in your last post. Those are not encrypted.

Cadence Incisive or NCLaunch (same thing) is listed as a supported simulator for the Ethernet IP (shown in your previous post).

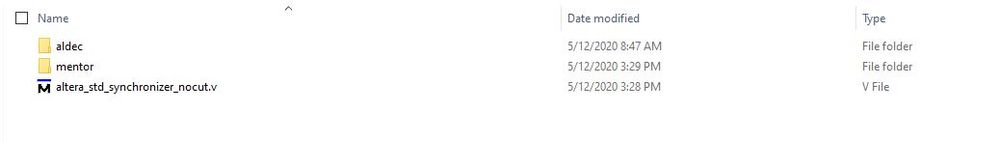

When the IP is generated there is a /submodules directory containing all the encrypted components of the Ethernet broken out by simulator ./Aldec and ./Mentor but nothing for Cadence.

Cadence cannot decrypt files that are encrypted for Mentor or for Aldec (as far as I can tell, decryption fails when I try it).

So my question again is, Why are the Cadence submodules not generated and how can I get them?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Travis,

It's good to clarify the problem statement again.

- Now we are aligned that Cadence NCSIM or NCLaunch is the right sim tool to use

- Regarding your question on "Why are the Cadence submodules not generated and how can I get them ?"

- This is the part that confused me. I used Quartus v19.1 standard edition to open up your earlier TSE QSYS design file, generate verilog sim model design files and I can see that cadence sim submodules design files are generated as per attached pic. These are cadence encrypted design files, not Mentor or Aldec

- Are you saying you faced some issue in generating "cadence sim submodules design file ?" where you see different outcome as compare to my screenshot pic ? Can you show me your screen shot to highlight the issue to me ?

- Or you managed to generate "cadence sim submodules design file" but faced problem compiling these design in Cadence NCSIM ? Then can you show me the error log ?

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok now we are getting somewhere. My submodules folder does not contain all the files that yours does.

The next post shows what the Quartus Generated /submodules folder looks like on my system.

Note that there is nothing for Cadence.

I have tried Quartus Standard 18.0,19.1 even 16 but none of them generated the Cadence folder on my laptop (Windows 10).

Do you have any ideas?

Possibly I could get them from you directly through a dropbox or something like that?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Travis,

This is weird.

I believe our only difference is you are using Quartus Win version while I am using Quartus Linux version.

I don't want to rush into sharing with you linux cadence submodules files in case it create new issue .

Let me validate this issue with Quartus Standard v19.1 Win first.

Then I will get back to you.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, thanks. I might be able to try the Linux version on another machine. I'll let you know if I can get that going.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dlim, I succesfully generated the /cadence submodules folder and ran the simulation on a Linux machine. So there is definitly a bug in the Windows version of Quartus Standard.

Thanks for your help figuring this out.

Travis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Travis,

It's good to know you got it working in Linux.

I need to find out more internally whether there is different sim tool support plan between Linux and Win or it's just purely a bug in Quartus Win

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Travis,

I carefully read back the EDA support plan table from Quartus release note doc and finally found out the answer is there all the while. Sorry, I didn't catch it earlier.

Let me attached the screen shot and explain to you again.

- For Cadence sim (IES) for both Quartus std and pro, there is bracket (64-bit Linux only) – I understand now this is referring to support in Linux OS only

- If we look at Mentor Modelsim SE, it’s bracket (64-bit only) – this means it’s supported on both Win OS and Linux OS

- If we look at Aldec Active-HDL, it's bracket (32 bits win only) - this means it's supported in Win OS only

I hope I clarify your doubt now.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dlim, thanks for looking into this further. I have to disagree with your assessment of Table 5 from the release notes. I believe it is referring to simulator support for launching the simulator from within Quartus. For example, going to tools/launch simulation library compiler. This makes sense since Cadence does not produce a Windows product.

But I am not trying to open Cadence from Quartus and it does not address the issue of the missing submodule files.

However when you look at the Triple-Speed Ethenet User guide v 19.4 page 171; both Cadence Xcelium and plain Cadence are listed as supported and it shows the files that should be produced. The Windows tool does produce those the files listed in table 111. However those files are useless without the submodule files that only the Linux version produces. So why would it produce some of the files but not all?

To summarize I still believe this is a bug. Since the Ethernet user guide shows Cadence as supported but the Windows version does not produce all the necessary files for this IP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Travis,

I have clarified with TSE engineering developer team.

- It's not a bug as TSE IP has no plan to support Cadence in Win OS as mentioned in Quartus release note doc.

- All Intel FPGA IP solution sim support plan needs to be align with Quartus support plan in general unless special clarified in respective IP user guide doc.

What you mentioned in both TSE IP user guide doc and IP sim generation script indeed is a flaw that Intel needs to improve on.

We are working internally to see how we can provide better clarification and user experience to customer moving forwards.

For now, I hope that you can move on with your project development using Linux OS first.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for tracking that down. Hopefully the documentation can be made more clear soon for other users.

I am able to proceed on my end.

Thanks again,

Travis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Travis,

Yup, I will definitely work out the improvement plan with Intel team internally.

Alright, I will be setting this case to closure shortly.

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page