- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm working on simulation with IP cores and having issue with unbound components. Specifically, the Questa compiler complains about the dcfifo mixed width have declared and instantiated interface aren't matched. It doesn't error out the simulation but it creates undefined status signal, such as fifo empty and full, which are used to constraint other control signal like fifo read and write.

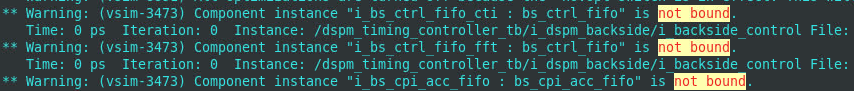

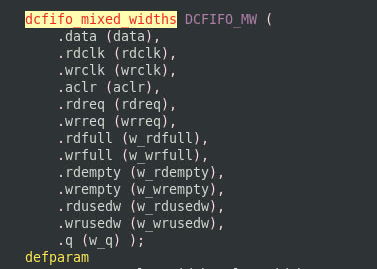

The two screenshots below show the bs_ctrl_fifo unbound warning. bs_ctrl_fifo is ip cores that instantiate dcfifo, which instantiate dcfifo_mixed_width.

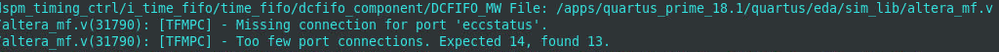

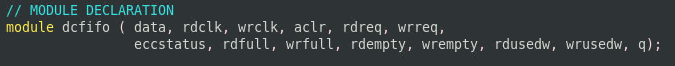

I open the /apps/quartus_prime_18.1/quartus/eda/sim_lib/altera_mf.v and find dcfifo entity as below. The entity has eccstatus signal.

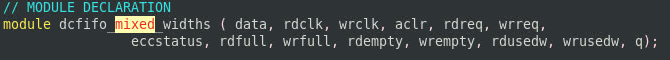

In the same file, dcfifo_mixed_widths is also found. The entity has eccstatus signal.

However in the instantiated interface of dcfifo_mixed_widths, there is no eccstatus signal. I think that's what Questa compiler complains about. I acknowledge that we use the already compiled simulation library, and I assume the source code and compiled simulation library are matched.

There are many more ip cores that has the same warnings.

Some information that may help:

- Questa 10.5c

- Quartus Prime 18.1

- VHDL 2008

- A10 FPGA

Please let me know what else is needed to help identify the issue.

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Which ip core you're using?

which language you're using for ip generation?

Quartus 18.1 lite or standard or pro?

Have you try simulation with mentor msim_setup.tcl before?

Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

Thanks for reaching out. From the qsys file, <module name="fifo_0" kind="fifo" version="16.1" enabled="1" autoexport="1">, <parameter name="hdlLanguage" value="VERILOG">. It wraps around dcfifo, which instantiate dcfifo_mixed_width. I notice the fifo version is 16.1 and the Quartus Prime version is 18.1.0

From the Help menu of the GUI : Quartus Prime Version 18.1.0 Build 625 09/12/2018 SJ Standard Edition

We use qsys-generate to regenerate the core files from qsys files, which are checked in to git repo, then use msim_setup.tcl to generate simulation libraries for the cores.

Thanks,

-Minh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Minh,

Check out this document https://faculty-web.msoe.edu/johnsontimoj/EE3921/files3921/ug_fifo.pdf (page 31) onwards.

You can turn on FIFO Embedded ECC feature by enabling enable_ecc parameter in the FIFO Intel FPGA IP GUI.

Embedded memory ECC feature is only available for M20K memory block type.

When you enable the ECC feature, a 2-bit wide error correction status port (eccstatus[1:0]) will be created in the generated FIFO entity.

Best Regards,

Sheng

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution and give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

Thanks for your response. So the fifo won't work with ECC disable? Is the memory block type must be M20K for the fifo to work? The design has been deployed already and the testbench is being developed for future expansion purposes. We prefer to minimize the change to IP cores as much as possible.

Thanks,

-Minh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Minh,

Check out this https://www.intel.com/content/www/us/en/support/programmable/articles/000081035.html.

I simulate the fifo using testbench system and don't get any not bound warning for missing port 'eccstatus'. See the file attached.

Does it affects your simulation result? If not probably you can just ignore the missing port 'eccstatus' warning.

Best Regards,

Sheng

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution and give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Minh,

May I know any further updates or concerns on this thread or do you need further helps on this case?

Thanks,

Best Regards

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Since there are no further feedback for this thread, I shall set this thread to close pending. If you still need further assistance, you are welcome reopen this thread within 20days or open a new thread, some one will be right with you. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page