- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I need info about electrical idle When we are in Reserve Serial Loopback(Metalic).

whether tx is disabled during electrical idle is receiving on Rx line or will be consider as 1 or 0 and transmitted on tx line

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. Please see my responses as following:

Here my query is when our S10 SERDES is RSL mode, if HW1_RX1 is receiving combination of data's and electrical idle, same SERDES HW1_TX1 will transmit same data's and electrical idle or not?

[CP] As I understand it, with the pre-CDR reverse serial loopback, the data received by RX buffer will be loopback to the TX buffer to be transmitted out. When the HW1_RX1 is receiving electrical idle, there will be no data passing to the TX buffer.

Due to no specific characterization or detail in the user guide, I am not sure what will be the HW1_TX1 output state. You might need to perform a test on hardware to tell. Sorry for the inconvenience.

Note that the different loopback modes are generally for debugging purpose only. It is not meant for production usage.

Please let me know if there is any concern. Thank you

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you have some inquiries related to the S10 L-Tile transceiver. Sorry for any confusion. Would you mind to further elaborate on your specific inquiries. You seems to mention about electrical idle and reverse serial loopback at the same time. Generally when we are using reverse serial loopback for debugging purpose, we need the TX buffer to be working.

Specific to electrical idle, when the TX PMA is put into electrical idle, there will be no data transmitted out from the TX.

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@CheePin_C_Intel

Thanks for response.

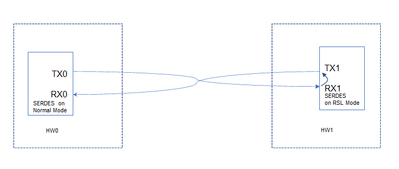

Consider we have two HW HW0 & HW1

HW0 SERDES is working on Normal mode

HW1 SERDES is on RSL Mode

HW0_TX0 is cable of transmitting the data for some duration and go back to electrical idle for some duration and process will be in loop with different data. Verifying same on HW0_RX0 side

HW1 SERDES is in RSL, we are expecting the data on HW1_TX1 will be same like HW0_TX0, combination of data and electrical idle

am i correct?

Here my query is when our S10 SERDES is RSL mode, if HW1_RX1 is receiving combination of data's and electrical idle, same SERDES HW1_TX1 will transmit same data's and electrical idle or not?

whenever we are receiving electrical idle on HW1_RX1 , whether HW1 SERDES TX1 will be disabled or do something to reflect electrical idle on tx line?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. Please see my responses as following:

Here my query is when our S10 SERDES is RSL mode, if HW1_RX1 is receiving combination of data's and electrical idle, same SERDES HW1_TX1 will transmit same data's and electrical idle or not?

[CP] As I understand it, with the pre-CDR reverse serial loopback, the data received by RX buffer will be loopback to the TX buffer to be transmitted out. When the HW1_RX1 is receiving electrical idle, there will be no data passing to the TX buffer.

Due to no specific characterization or detail in the user guide, I am not sure what will be the HW1_TX1 output state. You might need to perform a test on hardware to tell. Sorry for the inconvenience.

Note that the different loopback modes are generally for debugging purpose only. It is not meant for production usage.

Please let me know if there is any concern. Thank you

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page