- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sir/ Madam,

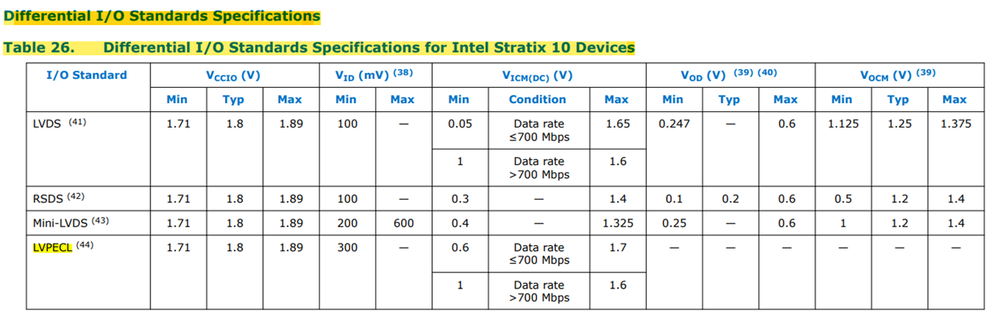

I understand Intel Stratix 10 board can receive a PMA4 signal (Data rate from 2 Gbps to 57.8 Gbps). The I/O standard is LVPECL, the below picture is the LVPECL 's specification and shows the VICM,VID. But I still feel confused. PAM4 signals have 4 voltage levels. Could you please further explain the specifics for each level?

For example, the demands for eye width, eye height, eye nonlinearity, and SNDR(Signal to noise and dispersion ratio) .

Below is the introduction of LVPECL. A full document can be found in the below link (page 27)

If you have any test document about his PAM4 FPGA, there will be very helpful for us to understand the question.

Thank you so much! Please feel free to let me know if you have any comments.

Best regards,

Lily

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

PAM4 is new industry standard signal modulation technique, not something developed by Intel FPGA.

You can search in Internet to learn more about PAM4.

I found out below application note that explained on PAM4 that you can read further as well.

Thanks.

Regards,

dlim

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

PAM4 is new industry standard signal modulation technique, not something developed by Intel FPGA.

You can search in Internet to learn more about PAM4.

I found out below application note that explained on PAM4 that you can read further as well.

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page