- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

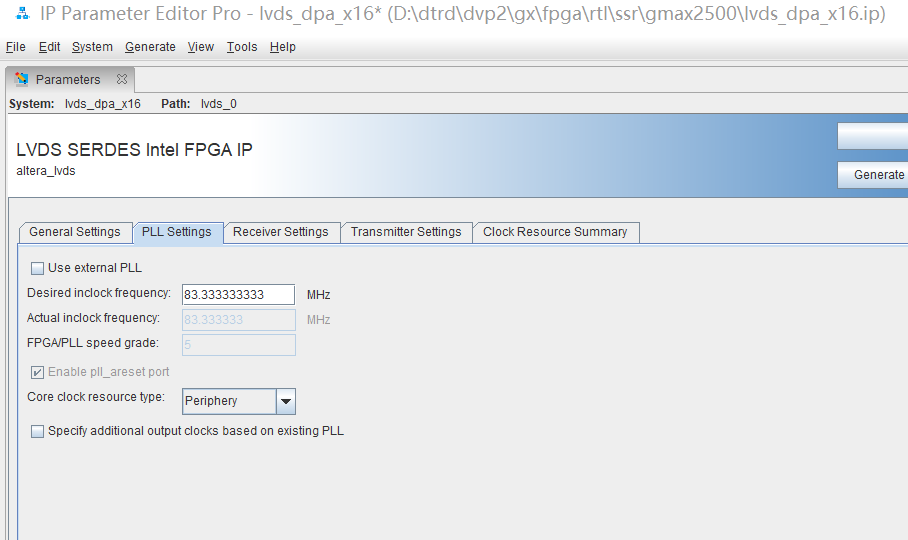

Error(18694): The reference clock on PLL "u_gmax2500|u_lvds_dpa_x16|lvds_0|core|arch_inst|internal_pll.pll_inst|altera_lvds_core20_iopll", which feeds an Altera LVDS SERDES IP instance, is not driven by a dedicated reference clock pin from the same bank. Use a dedicated reference clock pin to guarantee meeting the LVDS SERDES IP max data rate specification.

之前17.2编译没问题的,现在换成了19.4报这个错误

这个参考时钟输入是来自于另一个PLL的输出

Link Copied

2 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @FZhao12 You will need to assign it to a dedicated clock input pin on the same bank. I remember that newer version will block you from using IO pin as clock input to avoid your LVDS SERDES not performing up to specification.

Hope this answers your questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks There are no other questions for the moment

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page