- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm using an Arria V FPGA with an TSE IP.

The IP is configured for PCS only with SGMII output.

By definition, an SGMII interface has a differential data signal and a differential 625 MHz clock signal.

The differential serial data output of the TSE IP is named: "txp".

But where is the 625MHz clock ? Doesn't the IP generate one ?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

I can see that you are interested with Intel FPGA TSE IP recently.

For a start, you can always refer to TSE IP user guide doc where you should be able to find most of the info there to answer your doubt.

To answer your question, TSE IP doesn't enable SGMII interface as external port. It's hidden inside TSE IP.

The Txp port is the transceiver PMA port pin that you enable in TSE IP.

I have put together the explanation in below diagram

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm sorry but this doesn't answer my question.

I'm using the TSE IP with GXB. The txp and rxp is are serial SERDES pins.

But where is the 625 MHz clock that's supposed to be sent to the external device?

I expect the data to be sent together with this clock (source synchronous).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry, I didn't explain it clearly.

When you enabled GXB in TSE IP, you are operating in High Speed Serial Interface mode, not really in SGMII mode.

For serial interface application, the clock is already embedded inside the data bus itself. Therefore, you don't need extra sync clock anymore.

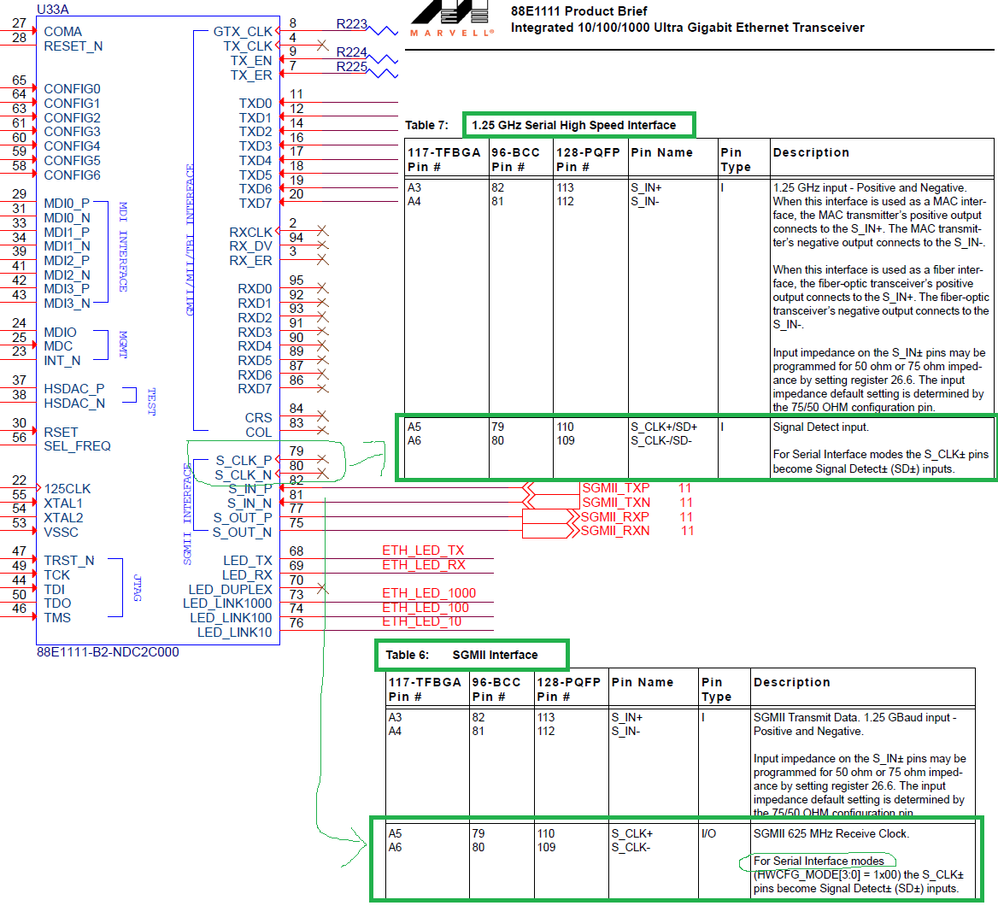

Attached is the screenshot of Intel FPGA dev kit board External PHY chip connection and PHY chip datasheet explanation.

I hope I clear your doubt this time.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

I am setting this case to closure since I didn't hear back further from you since my explanation in early July.

I hope I have cleared your doubt.

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page