- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

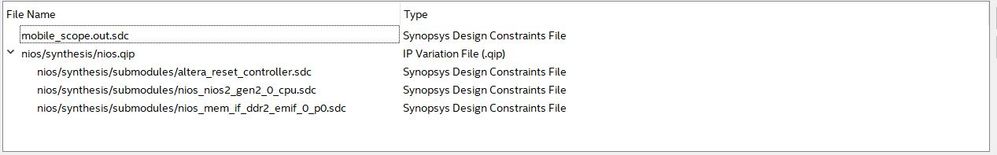

Project: NIOS + DDR2 UniPHY + other defined module by me.

After I set clock in SDC file, I find all inputs and outputs constraint are done.

In fact, I did not inputs and outputs.

It seems automatic generated by UniPHY SDC file covered inputs and outputs.

Question:

1) I think UniPHY IP SDC file only covers I/O related to memeory, why it impacts other I/O ? such as some ADC, spi bus, emmc interface....

2) I need to define timing constraint condition in my project SDC for other I/O, will it be ignored by Quartus due to exist UniPHY IP SDC?

Link Copied

0 Replies

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page