- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

in my current Arria 10 GX design I have one small Micron flash for the FPGA binary (MT25QU256ABA1EW9, 32MByte) and two larger Micron flash devices (MT25QU01GBBB1EW9, 128 MByte each) for random data.

I can write, read and erase the smaller flash via the GSFI without any problem.

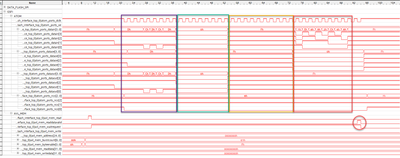

When reading one of the larger flash I only get back zeros via the Avalon-MM memory slave of the GSFI, but I can clearly see that there is data transferred on the SPI bus when I watch it in SignalTap, as seen below.

Purple box: Command (8 clock cycles, 1 Byte)

Green box: Address (8 clock cycles, 4 Byte)

Yellow box: Dummy cycles (10 clock cycles)

Red box: Readdata from flash (8 clock cycles, 4 Byte) - content: 0x87654321

Red circle: Readdatavalid from GSFI - content: 0x00000000

Unfortunately I can't watch the read transfer from the smaller program flash, because the SPI pins are not exported from the GSFI.

The CSR registers of the GSFI and the flash registers are initialized the following way and identical for the smaller and larger flash devices:

- Activate 4-Byte addressing in flash:

- Write 0x000000B7 to flash command setting register (0x1C)

- Write 0x1 to flash command control register (0x20)

- Write 0x00000101 to control register (0x00)

- Write 0x1 to baud rate divider register (0x04)

- Write 0x0 to CS delay setting register (0x08)

- Write 0x00000AEB (10 dummy cycles & read opcode 0xEB) to read instruction register (0x14)

- Write 0x00022220 to operating protocols setting register (0x10)

I have seen a similar problem posted on here, but the solution (removing the SFL) doesn't work for me, because I don't instantiate one. (see Solved: Re: Re:Arria 10 can't read from flash via Generic Serial Flash Interface - Intel Communities)

Does anyone have a clue why the data seen on the SPI bus doesn't show up on the Avalon-MM memory slave readdata signal when readdatavalid is high?

Best Regards,

Florian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

thank you for the reply. It isn't necessary to check the project anymore, because it now works.

The problem was solved by switching from version 19.1 to 21.1 of the Quartus Prime Standard software.

Best Regards,

Florian

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am still investigating this issue with engineering. I will get back to you once I have the solution to this issue.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Farabi,

I have read, that you'll get back to me as soon as you have the solution, but I just wanted to ask whether there is any news from engineering regarding the issue?

Best Regards,

Florian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

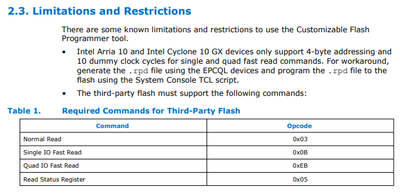

Please refer to link : https://www.intel.com/programmable/technical-pdfs/683271.pdf

Chapter 2.3 : limitation and restriction for customized programmer tool.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Farabi,

the restrictions mentioned in the document you attached don't seem to interfere what I am trying to achieve.

- I am using 4 Byte addressing

- I am using 10 dummy cycles

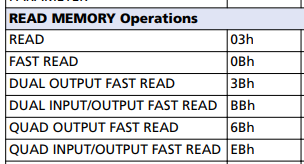

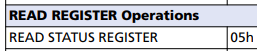

- The third party flash supports the four Opcodes mentioned in the document, as you can see her:

and

Can you explain what else I can learn from chapter 2.3 of the document you attached?

As mentioned in the original post above, the correct data is transmitted by the Flash via SPI, but the GSFI doesn't output it via the Avalon-MM slave.

Best Regards,

Florian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

To speed up debugging work, do you have a test case where we can replicate the issue at our end?

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

what exactly do you need to replicate the issue?

Do you need a project that includes the component that interacts with the GSFI or is the source code of the component sufficient?

Best Regards,

Florian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Farabi,

I'd like to bump the thread up again, because I am pretty stuck with this issue and it doesn't seem to be an hardware bug, because I can clearly see the correct SPI response in SignalTap (see my original post).

What do you need to replicate the issue?

Best Regards,

Florian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am sorry for late reply. Yes, I need a project that includes the component that interacts with the GSFI is sufficient.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

thank you for the reply. It isn't necessary to check the project anymore, because it now works.

The problem was solved by switching from version 19.1 to 21.1 of the Quartus Prime Standard software.

Best Regards,

Florian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Good to hear that your design works at 21.1. The bug must have been fixed in 21.1.

I will file kdb to share with others, to help other customers.

If there is no further question, please let me set this case to close pending.

Thank you,

Farabi

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page