- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have two projects with an Cyclone 10lp16k FPGA using the VIP ip cores from intel. I develop with the Quartus Prime Lite 20.1 version (Windows).

In the first project, compilation and fitting worked fine. The second always abort during fitting.

I get this error:

Error (332000): can't read "fifo_type": no such variable

while executing

"string compare $fifo_type "d""

("foreach" body line 20)

invoked from within

"foreach inst $instance_list {

set hier_to_block ${inst}|input_fifo

set fifo_name ${hier_to_block}|*

This variable is checked in several .sdc files in the "db" folder during fitting.

Like i mentioned, i have two projects using the vip ip cores. This problem first did just occured on one of them.

The first one worked fine and has several platform designer subsystems with vip cores. if exclude some of them from build and i got the same error during fitting.

It seems to me that the variable "fifo_type" doesn't get always set correctly.

Is there is any way to set the variable manually?

If i delete all ".sdc" files with the fifo_type-check befor the fitter starts, fitting can finish. But im not sure if the design will work correct .

With best regards

Sebastian Schmitz

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

May I know do you able to isolate which VIP IP solution and which parameter setting in the IP is causing fitter error here ?

Also can you shared with me both your fitter passed and fitter failed Quartus design QAR file so that I can duplicate failure in house and debug them ?

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I assume that the clocked video output ip core cause the problem.

I prepared 2 projects, one works fine. the other will fail during fitting.

If you remove the "alt_vip_common_fifo.sdc" file in "db\ip\TPG\submodules\modules\alt_vip_common_fifo\src_hdl" before fitting the failing one should also work.

Both projects are basically the same. There is one Platform Designer subsystem "TPG" with just a Testpattern Generator and an Clocked Video Output and a second subsystem for video processig with a CVI - Clipper - Framebuffer -SDRAM Controller and CVO.

If you include the Video pipline the project will compile fine , if you comment it out it will fail during fitting.

With best regards

Sebastian Schmitz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks.

Let me take a look on both designs.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sebastian,

I wouldn't advise you to remove the sdc constraint else I worry it may impact the VIP functionality.

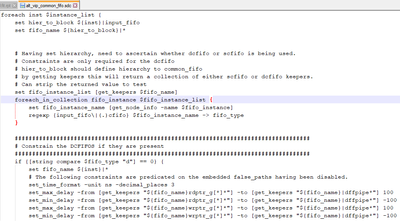

I looked the sdc file constraint as per attachment. Looks like it's detecting data input to decide whether it should perform additional timing constraint for DCFIFO or not.

I know you are seeing fitter error due to the nature of how the SDC constraint file is written but since after providing user logic data input to the VIP suite IP then the fitter error will be gone.

- In your actual project development, I do expect you will be supplying data to VIP suite IP to process the video data accordingly as well

I know it's not perfect but do you still a problem while working on your actual Quartus design development when you supply actual video data to VIP suite IP ?

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sebastian,

I didn't hear back from you.

I presume your project development should be ungated once you provide data input to VIP suite IP. (no more fitter error)

For now, I am setting this case to closure.

Thanks for your understanding

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for gettig back to you so late. Thanks a lot.

I now understand when this bug shows up. You're right, at a futher advanced state of the firmware the problem will solve itself and the bug should not show up.

For now i just have custom components for video processing. To get rid of this fitter error i kicked the vip testpattern generator and replaced it by a custom one.

With best regards

Sebastian Schmitz

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page