- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

we tried to generate ddr3_lower with ECC option . we had doubts on whether separate data pin will be allocated for ECC or not. to confirm that we need example file.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

There is no special example design for ECC enablement but I can explain how DDR3 IP manage ECC option.

In DDR3 IP,

- If user set DQ = 40 with controller ECC option ON

- DQ [39:32] will be the ECC bit

- If user set DQ = 72 with controller ECC option ON

- DQ [71:64] will be the ECC bit

Meaning if ECC option is turned on, the last 8 DQ bit will be the ECC bit.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply. For our confirmation , we need to use 45bit datawidth + 8 bit ECC . so we need to generate 64 bit ddr3 controller with ECC. Please confirm . If we try to generate 56bit DDR3 controller with ECC The error message which is shown in tool window is attached here. PFA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As the DDR3 IP error message explained, 45 bits is not a valid configuration for DDR3.

DDR3 SDRAM chip typically comes in either x4, x8 or x16 DQ data bits width. So, the valid configuration will always be multiply of 4, 8, or 16.

- For instance, to build x32 DQ configuration

- User can connect to 8 "x4 SDRAM" chip

- Or User can connect to 4 "x8 SDRAM" chip

- Or User can connect to 2 "x16 SDRAM" chip

I never encounter physical DDR3 SDRAM chip that can support 45 bits. That's why you see the error message as this is invalid configuration or none standard configuration

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply. We tried with 56 bit controller only not 45 bit(Please check the attached screenshot). our doubt is "which interface datawidth(48,56,64) should be selected for our required data 45 bit+8 bit ECC?".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, I can see you configured DQ = 56bits. DDR3 IP prompt error because this is invalid configuration setting

but I think you didn't get my point.

What I am trying to tell you is "45 bit+8 bit ECC" is invalid configuration because "45 bits DQ" is not a valid configuration at all.

- There is no option that you can set in DDR3 IP to accept either "45 bit+8 bit ECC" or "just 45 bits DQ without ECC".

- It doesn't make sense to support 45 bit DQ as I explained in previous post. There is no DDR3 SDRAM chip that support 45 bit configuration

The error message already explained the supported ECC option which is 16, 24, 40, 72

- 16 configuration = 8 DQ bit + 8 ECC bit

- 24 configuration = 16 DQ bit + 8 ECC bit

- 40 configuration = 32 DQ bit + 8 ECC bit

- 72 configuration = 64 DQ bits + 8 ECC bit

I hope I clear your doubt now

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

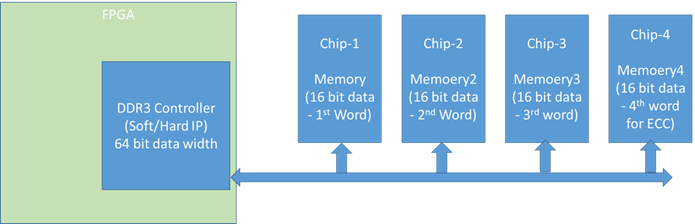

Yes, I understood that we cant use 45 + 8 bit ecc. But I am having doubt in how to map this 45 bit data + 8 bit ECC. I need to store 45 bits data in memory . if ecc enabled , 8 bit extra bits will be allocated. For this requirement, 64 bit controller only can be used. is this correct?

In 64 DQ pins, 0 to 44(data) and 56 to 63(ECC) Pins will be used. remaining DQ pins will be dummy data.

To store that data, 4x16 bit DDR memory going to be used. first 3 DDR memory will be used to store data.( refer below diagram for connection)

Can we connect last 8 DQ pins to first 8 bits of chip4.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The DDR3 IP configuration and on board SDRAM configuration needs to match else DDR3 will failed calibration.

Let me reiterate again - the supported ECC option in DDR3 IP is either 16, 24, 40 or 72.

- You cannot key in any other value when ECC option is on

- There is no 64 bits option with ECC on

- ECC bits will always be the last 8 bits of your DQ data bus, can't be in the middle of DQ bus

The only option that will works for your setup is as below

- 72 bits configuration = 64 DQ bits + 8 ECC bit

- DDR3 IP will generate 72 bits DQ bus connection

- On board SDRAM also needs to have 72 bits to match and connect to FPGA DDR3 72 bits

After that, if your user application just needs to use 45 bits then you need to add extra processing design to manually encode/decode padding of the rest of unused DQ bit to either 0 or 1. This is due to every DDR3 burst will send 72 bit.

- Typically user application can use Avalon bus byteenable feature to mask unused DQ data bit but that's control in byte form (8 bits per group)

- There is no control feature that can support unique 45 bits grouping. You need to create your own processing design

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page