链接已复制

Hi,

As I understand it, you are observing an issue with 5G LDPC IP in hardware where the signaltap seems to be showing sink_ready stuck at 0. To facilitate further debugging, would you mind to try to perform Modelsim simulation with your design to see if you can observe similar issue. If similar issue is observed, you may also cross check with the simulation example generated by the 5G LDPC IP to see if can spot any anomaly.

For your information, I have tested simulating the example design in Modelsim and seems like it is functioning.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

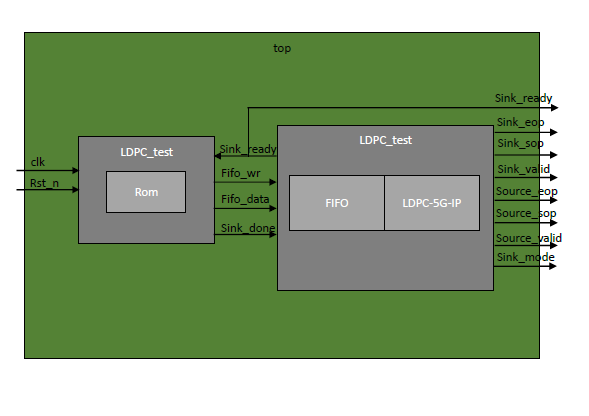

LDPC IP in my hardware has been verified in Modelsim, and the simulation has been successfully compared with MATLAB. Only when it is verified in FPGA, it is found that the sink ready signal is low. When I added the input and output signals to HDL for verification, I connected them to the pin except for the sink [data]. I found that in post fit, the compiler automatically connected the signals to GND. I confirm that my reset signal is normal. The signals about LDPC are all 0

Hi,

thanks for your update.

Would you mind to share with me a simple test design which could replicate your observation ie the signals connected to GND and also sink_ready stuck at low in hardware? I would like to look into it to see if can spot any anomaly.

Please feel free to let me know the specific device and devkit (if any) that you are using to replicate the observation?

Please share with me the specific steps that you are taking to replicate the observation or test the design. I would like to see if I can bring up a setup to replicate your observation.

Thank you.