- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hello,

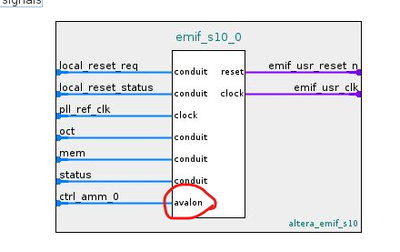

I have a design with two AV-MM read ports and one write port, including read_data_valid and write_data_valid, and separate watirequest for each port. All these three ports are master ports, which should be connected to slave ports.

I am wondering how I can instantiate an EMIF that can support this kind of design and have an arbiter to which I can connect all these three ports to it. I want to use the DDR4 protocol for my design.

I could not find anything useful in the UG of EMIF, and it is not clear in Platform Designer whether I can have this kind of interface or not.

I will be glad if somebody can help me with this issue.

Thanks,

-- Mahdi

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

FYI, master = host, slave = agent.

In Platform Designer, you can connect an agent interface to any number of host interfaces. The arbitration logic is automatically implemented in the generated interconnect. That's one of the handy features of using PD. Just make the connections in the usual way in the tool (dots in the Connections column or right-click an interface to select what it should be connected to) and generate the system.

Ссылка скопирована

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi Mahdi,

Thank you for submitting your question in Intel Community.

I'm Adzim will assist you in this thread.

Based on your design configuration, I think you can create your own custom memory controller.

The DDR4 EMIF IP can be generated either Hard PHY only or Hard PHY and Hard Memory Controller.

If you want to use your own memory controller, the EMIF IP can be generated in Hard PHY only configuration.

Regards,

Adzim

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Thanks for your reply, but my question is whether I can connect three AV-MM Master ports to this AV-MM slave.

If not, how can I do this?

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

FYI, master = host, slave = agent.

In Platform Designer, you can connect an agent interface to any number of host interfaces. The arbitration logic is automatically implemented in the generated interconnect. That's one of the handy features of using PD. Just make the connections in the usual way in the tool (dots in the Connections column or right-click an interface to select what it should be connected to) and generate the system.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Подписка на RSS-канал

- Отметить тему как новую

- Отметить тему как прочитанную

- Выполнить отслеживание данной Тема для текущего пользователя

- Закладка

- Подписаться

- Страница в формате печати