- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

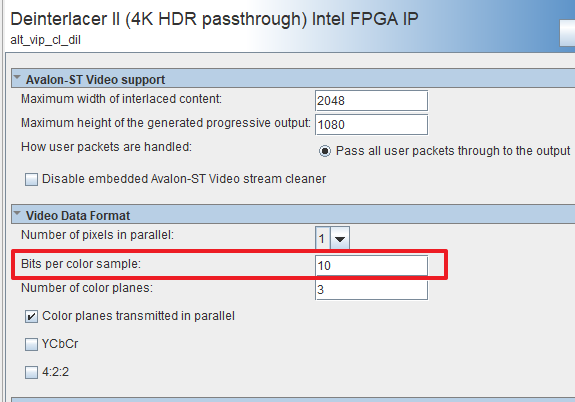

deinterlace II ip ,when i select 8bit or 12bit of color sample, my program is working properly, but when i select 10bit, is abnormal. The input is the same

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am not sure what colour format that you use. Have you try with different color format input ?

Are you using latest Quartus version else you can try upgrade to latest Quartus version to see if the issue still persist ?

Also you can try out different deinterlacing algorithm to see if it make a difference

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Unfortunately we don't have the example design.

Intel FPGA doesn't offer v18.2. I presume you are referring to v18.1.2 ?

To rule out potential old Quartus version issue,

- pls try to upgrade to latest Quartus version if possible.

- Since it's working on your colleague PC, you can install v18.1 on your PC to see if it's v18.1.2 version issue but I doubt so

Another thing to check is to ensure your FPGA design is timing clean to avoid design functionality failure

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

现在发现主要问题还是avalon-mm接口,发现deinterlace ip 出来的某次读突发会导致avalon-st接口的ready拉低一直不变,st接口按照协议打包正确,mm接口也是按照官方手册的时序进行操作的,但是有一点就是我同事的mm接口没有突发长度为1的时候,但是我这边频繁出现,官方对这个IP没有任何时序上的介绍,所以也不知道问题现在在哪

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

The timing diagram spec of all Video IP is shared and explained in chapter 2 of the VIP user guide doc. Feel free to check it out.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

发现当deinterlace ip参数设置中的Avalon-MM接口位宽设置为256bit时,屏幕就不显示,Avalon-ST接口的ready就拉起不来;而选择接口位宽为512bit时,但由于我的emif是320bit位宽,所以我只截取MM接口的低256bit进行读写DDR。最终显示图像的现象是文字会抖动,应该是少了一半有效数据的关系。

但为什么ip 选择256不行,而选择512可以?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

选择256和512以及128bit位宽有什么区别?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The bus bit width should only affect the operating frequency to maintain the same video bandwidth

- For instance, when the bus bit width x2, the operating frequency should be divided x 2

- when the bus bit width x4, the operating frequency should be divided x 4

If larger bus bit width works, I suspect your design could be facing timing closure issue where the data transfer can only happen safely with lower operating frequency

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

但是为什么512bit位宽是可以的?如果按照您的说法,更改位宽需要更大的频率,256bit不行,那么512bit也应该不行

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am not sure I am following your explanation here.

- Sorry, this is English forum so I am having tough time to understand chinese translation here

When bus width goes higher, the expected operating frequency should goes lower.

- Assuming bus width = 128, required operating frequency = 1x

- when bus width = 256, required operating frequency = 1x divide by 2

- when bus width = 256, required operating frequency = 1x divide by 4

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, typo in my earlier post

When bus width goes higher, the expected operating frequency should goes lower.

- Assuming bus width = 128, required operating frequency = xxx MHz

- when bus width = 256, required operating frequency = xxx MHz divided by 2

- when bus width = 512, required operating frequency = xxx MHz divided by 4

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page