- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi

I'm using a Arria 10 development kit with a DDR4 memory.

I want to enable a burst size of 1024 (the maximum the avalon bridge ip allows).

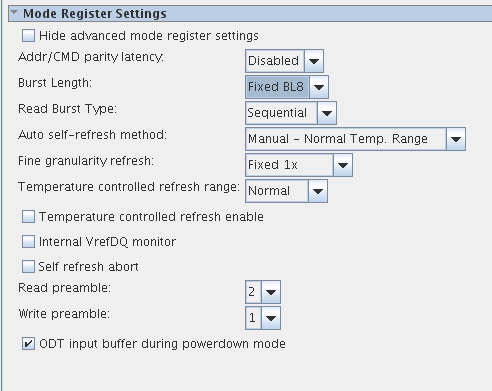

The EMIF connected to the HPS is configured to burst size of 8 ('fixed BL8') and cannot be changed in the gui:

- is there a way to configure this size?

- what will happen if the Avalon bridge connected to the HPS is with burst size of 1024?

thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sir,

I think there are misunderstanding. The BL that you are seeing in this GUI is the BL between FPGA and the SDRAM device.

I believe you are interest on the Burst length on the local interface (Avalone -MM).

If yes, it is actually support 128Bits. See this document:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20115.pdf#page=36

You do not need to set the local burst length value when you generate the IP. The IP will generate the local interface with the burstcount signals with 7 bits which is equal to 128.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, typo correction:

Hello Sir,

I think there are misunderstanding. The BL that you are seeing in this GUI is the BL between FPGA and the SDRAM device.

I believe you are interest on the Burst length on the local interface (Avalone -MM).

If yes, it is actually support BL up to 127. See this document:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20115.pdf#page=36

You do not need to set the local burst length value when you generate the IP. The IP will generate the local interface with the burstcount signals with 7 bits which is equal to 128.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi

thank you for the answer.

I tried reducing the burst size on the avalon MM bridges (Avalon MM Pipeline bridge IP) to 128 and 64, both did not work (when trying to read, the 'waitreq' asserts and stays high).

from what I understood from your answer this should work (when burst size was '1' it worked).

any ideas what may be the issue?

I'm working with data_size of 64 bit does that have any impact?

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, You can generate the example design and check how its work. Then compare with your traffic pattern and see any difference.

You also can run the simulation of the example design.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page