- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I instantiated an fPLL in the transceiver mode as I am using with the JESD204b IP. I noticed that the fPLL can't seem to be "reset" once the FPGA has been configured. Looking at the signaltap, I noticed that the pll_locked signal is always '1' even when the pll_powerdown signal is asserted, as shown in the screen capture below

If I disable the refclk going to this pll while still having the pll_powerdown signal at '1' , the locked signal goes to '0'. It is really as if this input is not connected to the pll on the fpga?

Is there something that I am not understanding ?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. Regarding your latest observation on the PLL powerdown, as I check with the registermap, there seems to be no issue with the registers that you are accessing.

Just to check with you on the following:

1. Just wonder if the "Enable capability registers" and "Enable control and status registers" under the Optional Reconfiguration Logic tab are checked in the fPLL IP core during instantiation?

2. If after performing #1, similar problem persists. Would you mind to help performing a Modelsim simulation to check on the functional behavior to see if the observation is consistent?

Please let me know if there is any concern. Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, still doesn't work (I added the line assignment, regenerated the fpll).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I guess I am just talking to myself on this intel forum. Hmm.

So I modified the generated vhdl file and set the enable_analog_resets => 1, now using signal tap, i can see that the locked signal behaves as expected when I put the fpll on powerdown. However I still have the problem

1. The clock to the refpin is active when the fpga is being configured : fpll locks after powerup, if I turn off the clock, it unlocks but if I turn the clock back on again, it locks again. So completely expected behaviour.

2. The clock to the refpin is inactive when the fpga is being configured : fpll NEVER locks after powerup.

Please, can somebody help me with this fpll behaviour ? Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. This case has just been routed to me.

As I understand it, your latest problem is related to fPLL not able to lock when there is no refclk present during device power up. For your information, in this case, you would need to perform the fPLL recalibration because the power up calibration cannot run correctly without refclk present during device power up.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your response.

Yes, the latest problem is exactly that. My current setup relies on a clock chip that needs to be configured first once the FPGA is loaded so having the transceiver ref clock running before the FPGA image is uploaded is quite complicated.

So to solve this problem, I would need to do the fPLL recalibration : To do this, do I need to enable the dynamic reconfiguration? Does it mean that I will have to manually write to the registers through, I guess, the avalon MM bus of the dynamic reconfiguration?

Thanks.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. Yes, you are right. You need to enable the dynamic reconfiguration and manual write to the AVMM registers. You may refer to "Fractional PLL Recalibration" in the A10 XCVR PHY user guide for further details on the registers to write to.

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I tried following the "7.5.2. Fractional PLL Recalibration " in the A10 XCVR PHY UG but it's very confusing.

First of all, by enabling the 'dynamic reconfiguration' on the fPLL, there is the avl mm bus with 10-bit address and 32-bit data. Are the addresses byte addresses or word addresses?

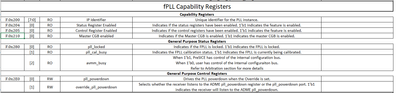

Because looking at the a10_registermap.xlsx (below is the excerpt), the addresses are not multiple of 4 which makes me think that they are word addresses? I can't seem to read and write to the fPLL and see anything. for example, looking at the signaltap locked output, i know that the fpll is locked but reading the "pll_locked" register, it just stays '0'.

How can I access these registers correctly then?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi again,

I finally figured out that the "7.5.2. Fractional PLL Recalibration " in the A10 XCVR PHY UG steps use byte addressing and I seem to be able to recalibrate the fPLL (the cal_is_busy signal can finally be toggled).

However I still don't know why the a10_registermap.xlsx doesn't have the same offset addresses for the fPLL. Why aren't they the same?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your update. Glad that you have managed to resolve the addressing and recalibrate your fPLL.

Regarding your latest inquiry on the register offset, as I look at the register map, seems like the address matches the user guide. Not sure if I have missed out anything. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Amongst the things that don't seem to correlate :

in the register map, at offset 0x280, bit [0] we should be able to read the 'pll_locked'. When I read at this offset, it always returns 0 even when the fPLL is clearly locked from the signaltap output.

at offset 0x2E0, if I wrote '3', I should be able to powerdown the fPLL and. However, looking at the signaltap output, this powerdown doesn't work (the locked signal is still '1').

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. Regarding your latest observation on the PLL powerdown, as I check with the registermap, there seems to be no issue with the registers that you are accessing.

Just to check with you on the following:

1. Just wonder if the "Enable capability registers" and "Enable control and status registers" under the Optional Reconfiguration Logic tab are checked in the fPLL IP core during instantiation?

2. If after performing #1, similar problem persists. Would you mind to help performing a Modelsim simulation to check on the functional behavior to see if the observation is consistent?

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Terima kasih lah, after enabling those options, now everything works as expected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. Glad that you have managed to resolve the problem.

I believe the initial inquiry has been addressed. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page